17 pci inbound comparison mask registers (picmrx), Table 9-17. pibarx field descriptions, Pci inbound comparison mask registers (picmrx) -43 – Freescale Semiconductor MPC8260 User Manual

Page 349: Pci inbound base address registers (pibarx) -43, Pibarx field descriptions -43, Figure 9-30, Pci inbound comparison mask registers (picmr x), Table 9-17. describes pibar x

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-43

in a PIBARx register causes a change in the GPLABARx in the base address bits that are non-masked by

PICMRx, and vice versa.

The system host is responsible for the configuration of the base address by writing to GPLABARx;

therefore, in PCI agent mode, the PIBARx registers should be read-only. However, if the PCI bridge is

defined as the PCI host, it may be easier to configure its own inbound base address by writing directly to

the PIBARx registers.

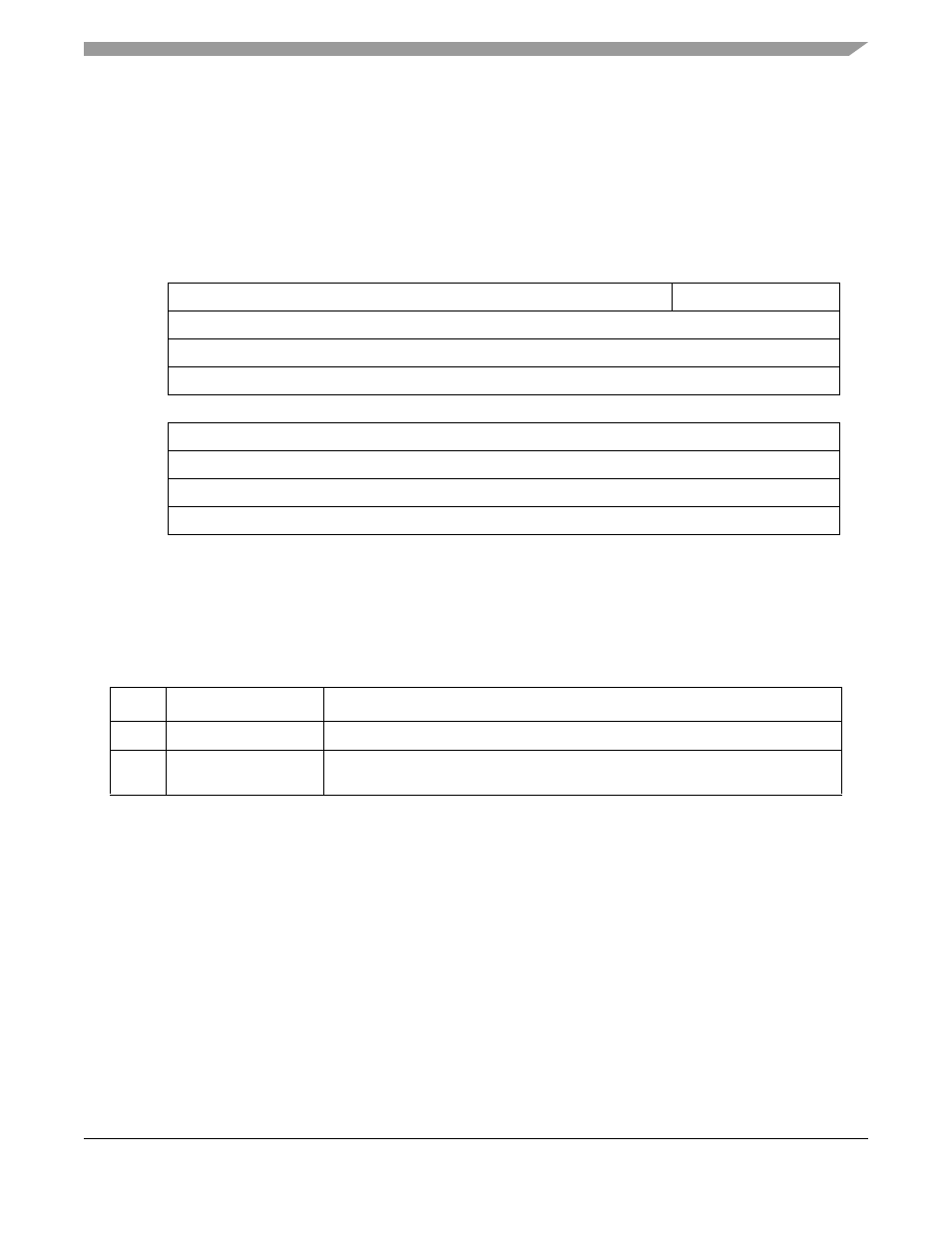

Figure 9-30. PCI Inbound Base Address Registers (PIBAR

x)

Table 9-17. describes PIBARx.

9.11.1.17

PCI Inbound Comparison Mask Registers (PICMR

x)

The PCI inbound comparison mask registers (PICMRx), shown in

, defines the inbound

window’s size. In PCI agent mode, this register should be initialized (either by the core or by the CP’s

automatic EPROM load) before the AGENT_CFG_LOCK bit (see

Section 9.11.2.22, “PCI Bus Function

) can be cleared to enable the host to configure the device. Some of the fields of this registers are

tied to the GPLABARx registers; see

Section 9.11.2.14, “General Purpose Local Access Base Address

31

20

19

16

Field

—

BA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108F2 (PITAR0); 0x108DA (PITAR0)

15

0

Field

BA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x108F0 (PITAR0); 0x108D8 (PITAR0)

Table 9-17. PIBAR

x Field Descriptions

Bits

Name

Description

31–20

—

Reserved, should be cleared.

19–0

Base Address

PCI address which is the starting point for the inbound translation window.This

corresponds to bits 31-12 of a 32-bit address