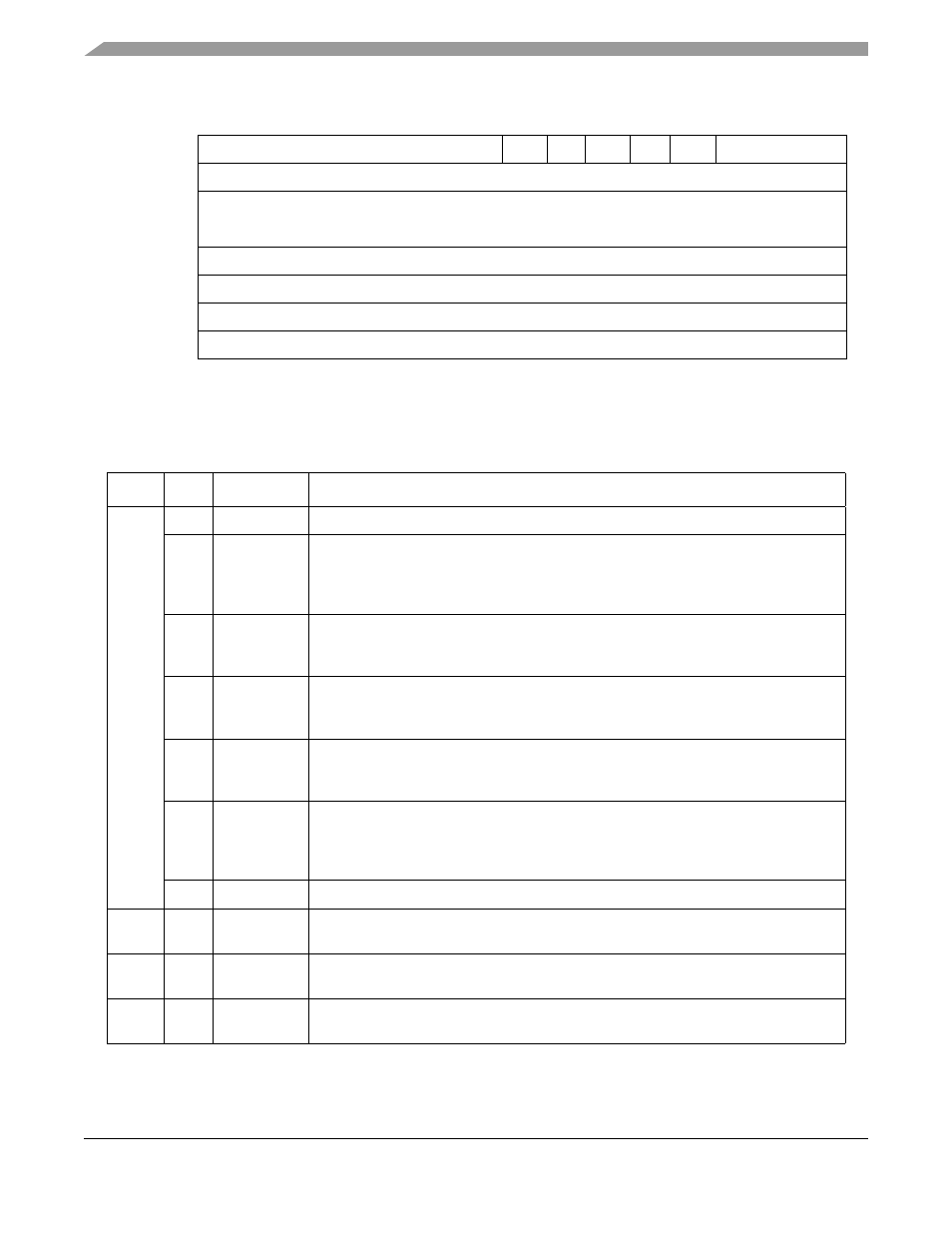

Figure 32-7. cps tx queue descriptor (txqd), Cps tx queue descriptor (txqd) -14, Cps txqd field descriptions -14 – Freescale Semiconductor MPC8260 User Manual

Page 1076: Figure 32-7, Table 32-2 describes the cps txqd fields

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

32-14

Freescale Semiconductor

describes the CPS TxQD fields.

.

0

7

8

9

10

11

12

13

15

Offset + 0x00

—

BNM

SW

HEC

CPS

TBM

—

Offset + 0x02

TxBD Table Offset In (switched mode only)

Offset + 0x04

TxBD Table Base

Offset + 0x06

Offset + 0x08

TxBD Table Offset Out

Offset + 0x0A

Number of Packets In Queue

Offset + 0x0C

NextQueue

Offset + 0x0E

—

Figure 32-7. CPS Tx Queue Descriptor (TxQD)

Table 32-2. CPS TxQD Field Descriptions

Offset

Bits

Name

1

Description

0x00

0-7

—

Reserved for internal use. (Used to save the BD status of the open BD.)

8

BNM

Buffer not-ready interrupt mask of the TxBD table.

0 The transmit buffer-not-ready event for this queue is masked. (The event is not sent

to the interrupt queue.)

1 The buffer-not-ready event for this queue is enabled.

9

SW

Switching queue.

0 Normal TX Queue.

1 This TxQD handles a switching queue. The receiver and transmitter share this queue.

10

HEC

HEC calculation.

0 Transmitter calculates the CPS header HEC.

1 The CPS header HEC is taken as is from the CPS buffer descriptor.

11

CPS

Sublayer type. For a CPS TxQD, this field must be set.

0 SSSAR or SSTED.

1 CPS packet.

12

TBM

Transmit buffer interrupt mask.

0 The transmit buffer event of this queue is masked. (The event is not sent to the

interrupt queue).

1 The transmit buffer event of this queue is enabled.

13-15

—

Reserved, should be cleared during initialization.

0x02

—

TxBD Table

Offset In

Used only when this queue is used for switching (SW=1). Should be cleared during

initialization.

0x04

—

TxBD Table

Base

This pointer points to the base address of the BD table.

0x08

—

TxBD Table

Offset Out

Holds the offset from the TxBD table base to the next BD to be opened by the

transmitter. Should be cleared during initialization.