Table 5-4. rmr field descriptions, 4 reset configuration, Reset configuration -6 – Freescale Semiconductor MPC8260 User Manual

Page 228: Rmr field descriptions -6, Section 5.4, “reset configuration, Ned in, Table 5-4

Reset

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

5-6

Freescale Semiconductor

5.4

Reset Configuration

Various features may be configured during hard reset or power-on reset. For example, one configurable

features is core disable, which can be used to configure a system that uses two PowerQUICC IIs, one a

slave device and the other a the host with an active core. Most configurable features are reconfigured

whenever HRESET is asserted. However, the clock mode is configured only when PORESET is asserted.

The 32-bit hard reset configuration word is described in

Section 5.4.1, “Hard Reset Configuration Word.”

The reset configuration sequence is designed to support a system that uses up to eight PowerQUICC II

chips, each configured differently. It needs no additional glue logic for reset configuration.

The description below explains the operation of this sequence with regard to a multiple-PowerQUICC II

system. This and other simpler systems are described in

Section 5.4.2, “Hard Reset Configuration

In a typical multi-PowerQUICC II system, one PowerQUICC II should act as the

configuration master while all other PowerQUICC IIs should act as configuration slaves. The

configuration master in the system typically reads the various configuration words from EPROM in the

system and uses them to configure itself as well as the configuration slaves. How the PowerQUICC II acts

during reset configuration is determined by the value of the RSTCONF input while PORESET changes

from assertion to negation. If RSTCONF is asserted while PORESET changes, PowerQUICC II is a

configuration master; otherwise, it is a slave.

In a typical multiple-PowerQUICC II system, RSTCONF input of the configuration master should be hard

wired to ground, while RSTCONF inputs of other chips should be connected to the high-order address bits

of the configuration master, as described in

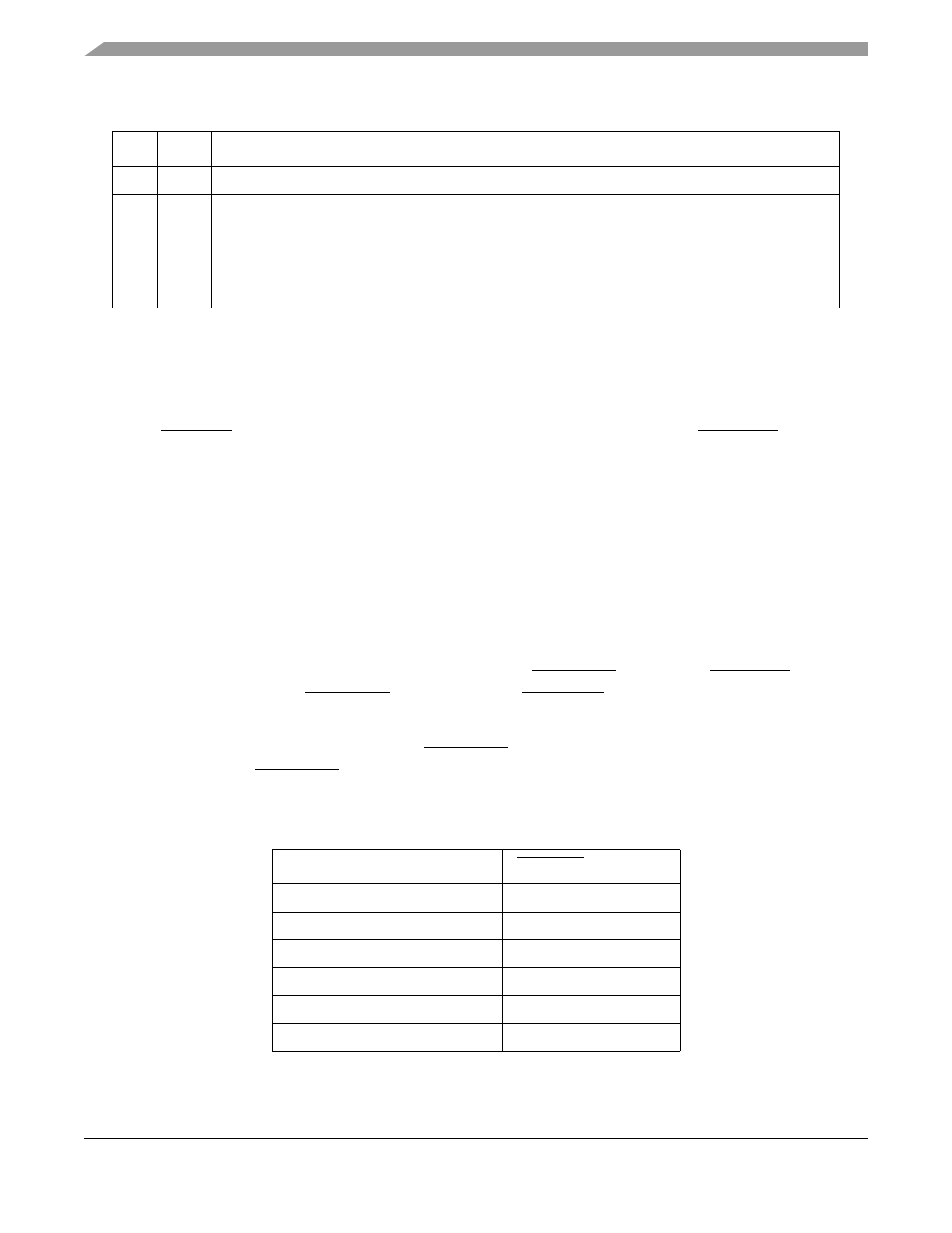

Table 5-4. RMR Field Descriptions

Bits

Name

Function

0–30

—

Reserved, should be cleared.

31

CSRE

Checkstop reset enable. The core can enter checkstop mode as the result of several exception

conditions. Setting CSRE configures the chip to perform a hard reset sequence whenever the core

enters checkstop state.

0 Reset not generated when core enters checkstop state.

1 Reset generated when core enters checkstop state.

Note: When the core is disabled, CSRE must be cleared.

Table 5-5. RSTCONF Connections in Multiple-PowerQUICC II Systems

Configured Device

RSTCONF Connection

Configuration master

GND

First configuration slave

A0

Second configuration slave

A1

Third configuration slave

A2

Fourth configuration slave

A3

Fifth configuration slave

A4