Figure 14-8. dual-port ram memory map, Dual-port ram memory map -19 – Freescale Semiconductor MPC8260 User Manual

Page 567

Communications Processor Module Overview

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

14-19

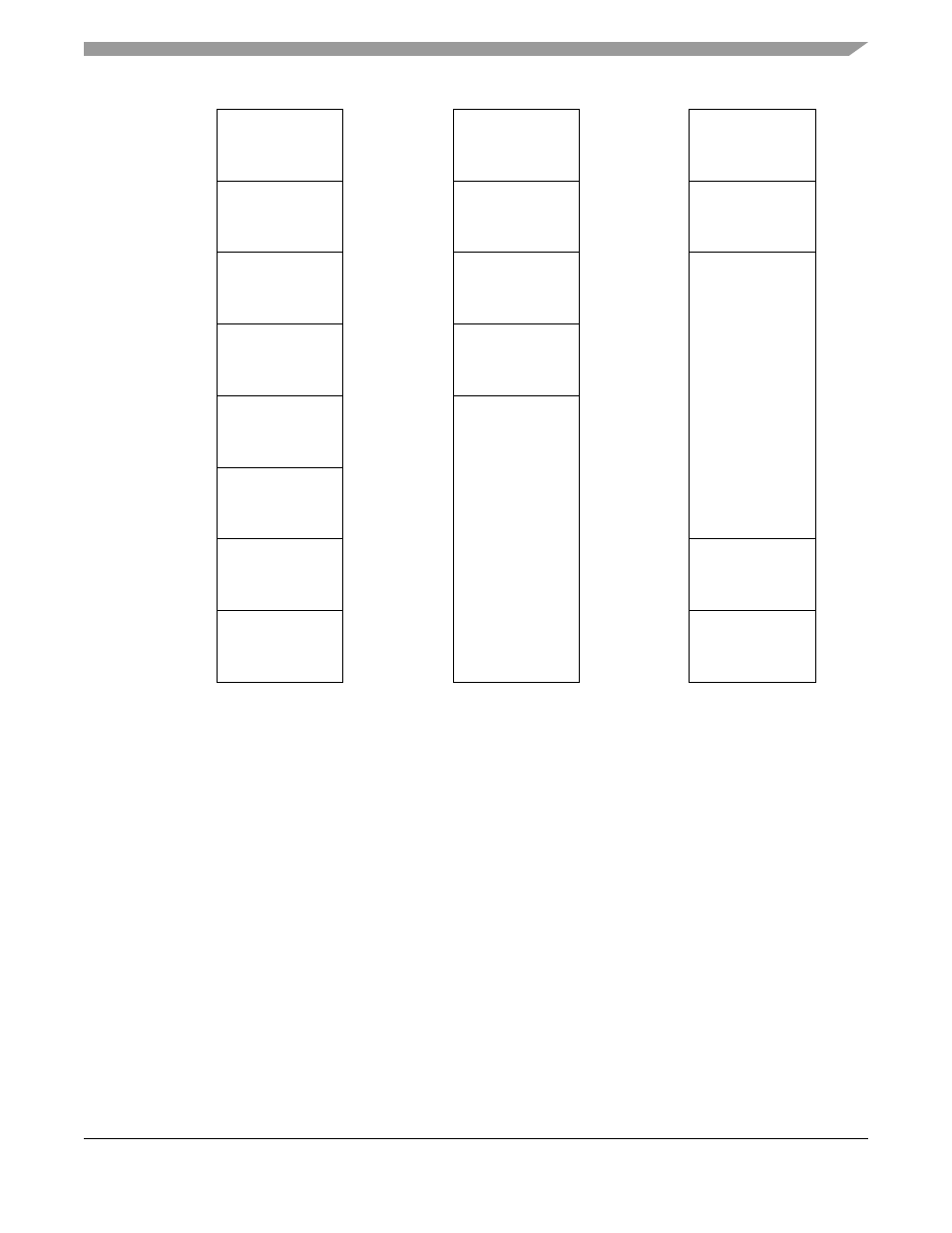

Figure 14-8. Dual-Port RAM Memory Map

The dual-port RAM data bus is 64-bits wide. The RAM is used for the following tasks:

•

To store parameters associated with the FCCs, SCCs, MCCs, SMCs, SPI, I

2

C, and IDMAs in the

parameter RAM.

•

To store buffer descriptors (BDs).

•

To hold data buffers (optional because data can also be stored in external memory).

•

For temporary storage of FCC data moving to/from an FCC FIFO (using the BTM) from/to

external memory (using SDMA).

•

To store RAM microcode for the CP. This feature allows Freescale to add protocols in the future.

•

For additional scratch-pad RAM space for user software.

The RAM is designed to serve multiple requests at the same cycle, as long as they are not in the same bank.

Only the parameters in the parameter RAM and the microcode RAM option require fixed addresses to be

used. The BDs, buffer data, and scratchpad RAM can be located in the dual-port system RAM or in any

BD/Data/µCode

2 KBytes

Bank #1

0x0000

BD/Data/µCode

2 KBytes

Bank #2

0x0800

BD/Data/µCode

2 KBytes

Bank #3

0x1000

BD/Data/µCode

2 KBytes

Bank #4

0x1800

BD/Data/µCode

2 KBytes

Bank #5

0x2000

BD/Data/µCode

2 KBytes

Bank #6

0x2800

BD/Data

2 KBytes

Bank #7

0x3000

BD/Data

2 KBytes

Bank #8

0x3800

Parameter RAM

2 KBytes

Bank #9

0x8000

Parameter RAM

2 KBytes

Bank #10

0x8800

BD/Data/µCode

2 KBytes

Bank #11

0x9000

BD/Data/µCode

2 KBytes

Bank #1

BD/Data/µCode

2 KBytes

Bank #1

BD/Data/µCode

2 KBytes

Bank #1

FCC Data

2 KBytes

Bank #11

0xB000

FCC Data

2 KBytes

Bank #12

0xB800

Reserved

(Partially Reserved)

Microcode

2 KBytes

1

Bank #13

0x4000

Microcode

2 KBytes

1

Bank #14

0x4800

Microcode

2 KBytes

1

Bank #15

0x5000

Microcode

2 KBytes

1

Bank #16

0x5800

0x6000

Reserved

1

Reserved on .29

µm (HiP3) devices.