Figure 8-5. address pipelining, 3 address transfer attribute signals, 1 transfer type signal (tt[0-4]) encoding – Freescale Semiconductor MPC8260 User Manual

Page 283: Address transfer attribute signals -9, Transfer type signal (tt[0–4]) encoding -9, Address pipelining -9, 1 transfer type signal (tt[0–4]) encoding

The 60x Bus

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

8-9

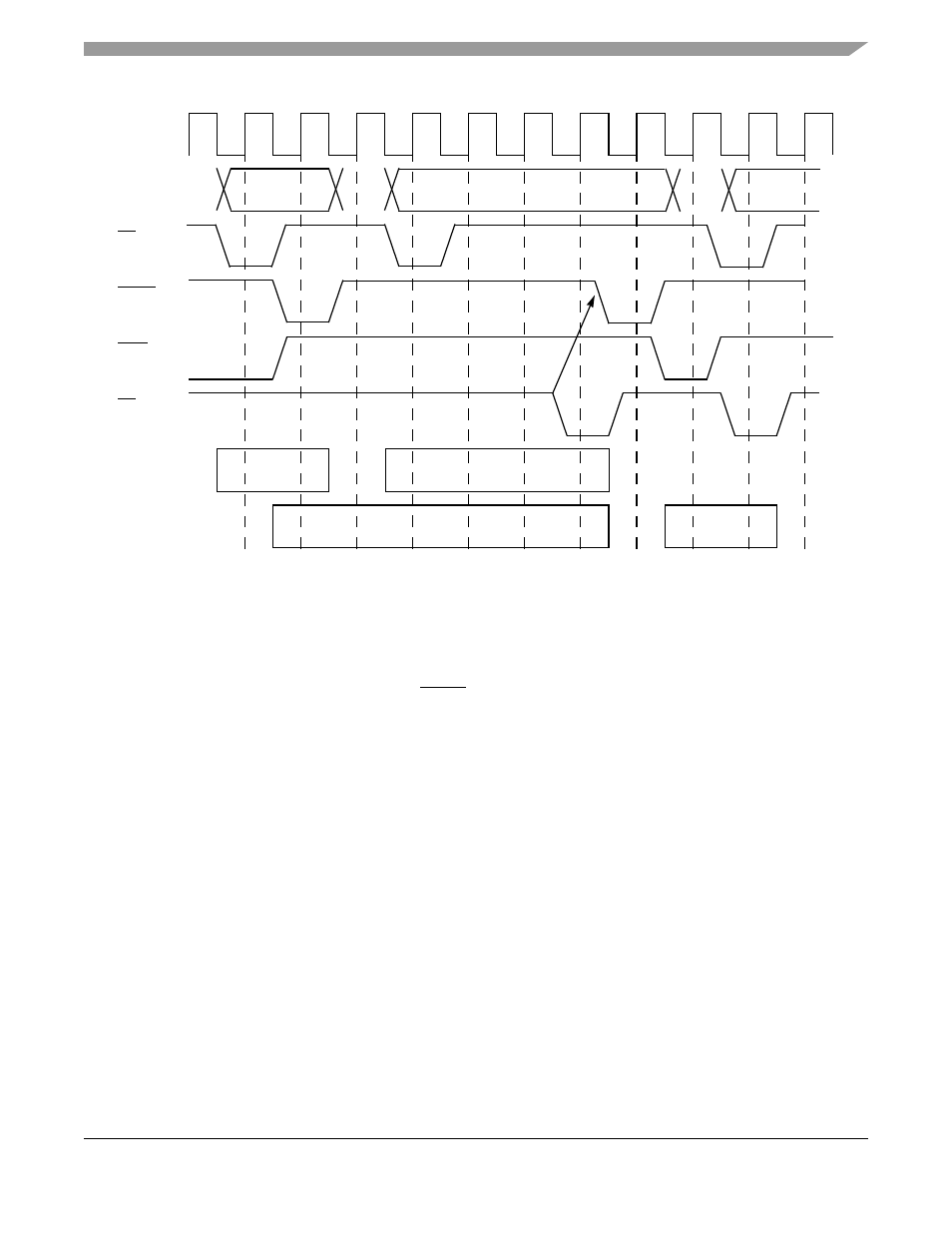

Figure 8-5. Address Pipelining

8.4.3

Address Transfer Attribute Signals

During the address transfer, the address is placed on the address signals, A[0–31]. The bus master provides

other signals that characterize the address transfer—transfer type (TT[0–4]), transfer code (TC[0–2]),

transfer size (TSIZ[0–3]), and transfer burst (TBST) signals. These signals are discussed in the following

sections.

8.4.3.1

Transfer Type Signal (TT[0–4]) Encoding

The transfer type signals define the nature of the transfer requested. They indicate whether the operation

is an address-only transaction or whether both address and data are to be transferred.

describes

the PowerQUICC II’s action as master, slave, and snooper.

CLKOUT

ADDR + ATTR

TS

AACK

DBG

TA

Address

Data Tenure

Tenure

Address 1

Data 1

Address 2

Data 2