3 interrupt queue parameter tables, Interrupt queue parameter tables -83, Interrupt queue entry field description -83 – Freescale Semiconductor MPC8260 User Manual

Page 1003: Interrupt queue parameter table -83, Ee section 30.11.3, Section 30.11.3, “interrupt queue parameter tables, Table 30-42

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

30-83

30.11.3 Interrupt Queue Parameter Tables

The interrupt queue parameters are held in parameter tables in the dual-port RAM; see

INTT_BASE in the parameter RAM points to the base address of these tables. Each of the four interrupt

queues has its own parameter table with a starting address given by INTT_BASE+ RCT/TCT[INTQ]

× 16.

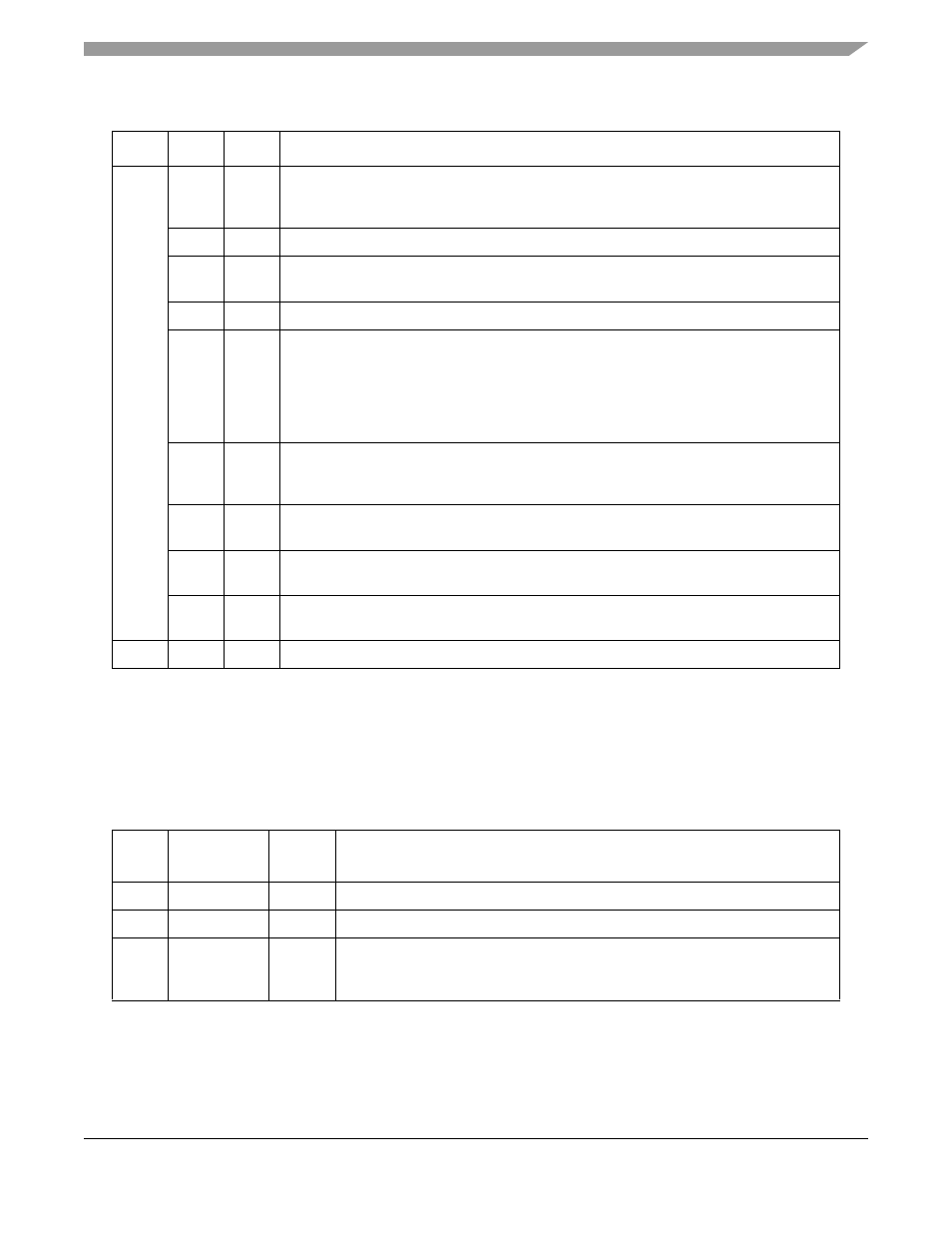

Table 30-42. Interrupt Queue Entry Field Description

Offset Bits

Name

Description

0x00

0

V

Valid interrupt entry

0 This interrupt queue entry is free and can be use by the CP.

1 This interrupt queue entry is valid. The host should read this interrupt and clear this bit.

1

—

Reserved, should be cleared.

2

W

Wrap bit. When set, this is the last interrupt circular table entry. During initialization, the

host must clear all W bits in the table except the last one, which must be set.

3–10

—

Reserved, should be cleared.

11

TBNR

Tx buffer-not-ready. Set when a transmit buffer-not-ready interrupt is issued. This interrupt

is issued when the CP tries to open a TxBD that is not ready (R = 0). This interrupt is sent

only if TCT[BNM] = 1. This interrupt has an associated channel code.

Note that for AAL5, this interrupt is sent only if frame transmission is started. In this case,

an abort frame transmission is sent (last cell with length=0), the channel is taken out of the

APC, and the TCT[VCON] flag is cleared.

12

RXF

Rx frame. RXF is set when an Rx frame interrupt is issued. This interrupt is issued at the

end of AAL5 PDU reception. This interrupt is issued only if RCT[RXFM] = 1. This interrupt

has an associated channel code.

13

BSY

Busy condition. The BD table or the free buffer pool associated with this channel is busy.

Cells were discarded due to this condition. This interrupt has an associated channel code.

14

TXB

Tx buffer. TXB is set when a transmit buffer interrupt is issued. This interrupt is enabled

when both TxBD[I] and TCT[IMK] = 1. This interrupt has an associated channel code.

15

RXB

Rx buffer. RXB is set when an Rx buffer interrupt is issued. This interrupt is enabled when

both RxBD[I] and RCT[RXBM] = 1. This interrupt has an associated channel code.

0x02

—

CC

Channel code specifies the channel associated with this interrupt.

Table 30-43. Interrupt Queue Parameter Table

Offset

1

Name

Width

Description

0x00

INTQ_BASE

Word

Base address of the interrupt queue. User-defined.

0x04

INTQ_PTR

Word

Pointer to interrupt queue entry. Initialize to INTQ_BASE.

0x08

INT_CNT

Half

Word

Interrupt counter. Initialize with INT_ICNT. The CP decrements INT_CNT for each

interrupt. When INT_CNT reaches zero, the queue’s global interrupt flag

FCCE[GINT

x

] is set.