5 peripheral interface, Table 14-2. peripheral prioritization (continued), Peripheral interface -7 – Freescale Semiconductor MPC8260 User Manual

Page 555: Peripheral prioritization -7

Communications Processor Module Overview

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

14-7

•

Many parameters are exchanged through the dual-port RAM.

•

The CP can execute special commands issued by the core. These commands should only be issued

in special situations like exceptions or error recovery.

•

The CP generates interrupts through the SIU interrupt controller.

•

The G2 core can read the CPM status/event registers at any time.

14.3.5

Peripheral Interface

The CP uses the peripheral bus to communicate with all of its peripherals. Each FCC and each SCC has a

separate receive and transmit FIFOs. The FCC FIFOs are 192 bytes. The SCC FIFOs are 32 bytes. The

SMCs, SPI, and I

2

C are all double-buffered, creating effective FIFO sizes of two characters.

shows the order in which the CP handles requests from peripherals from highest to lowest

priority.

NOTE: Emergency Prioritization

Elevation to emergency status (priority 4) is determined on per peripheral

basis and may depend on a peripheral’s mode of operation. Emergency

prioritization among peripherals maintains relative normal prioritization.

For example, simultaneous emergency requests from FCC1 transmit and

MCC2 transmit would be handled in the same order as normal requests

(FCC1 transmit).

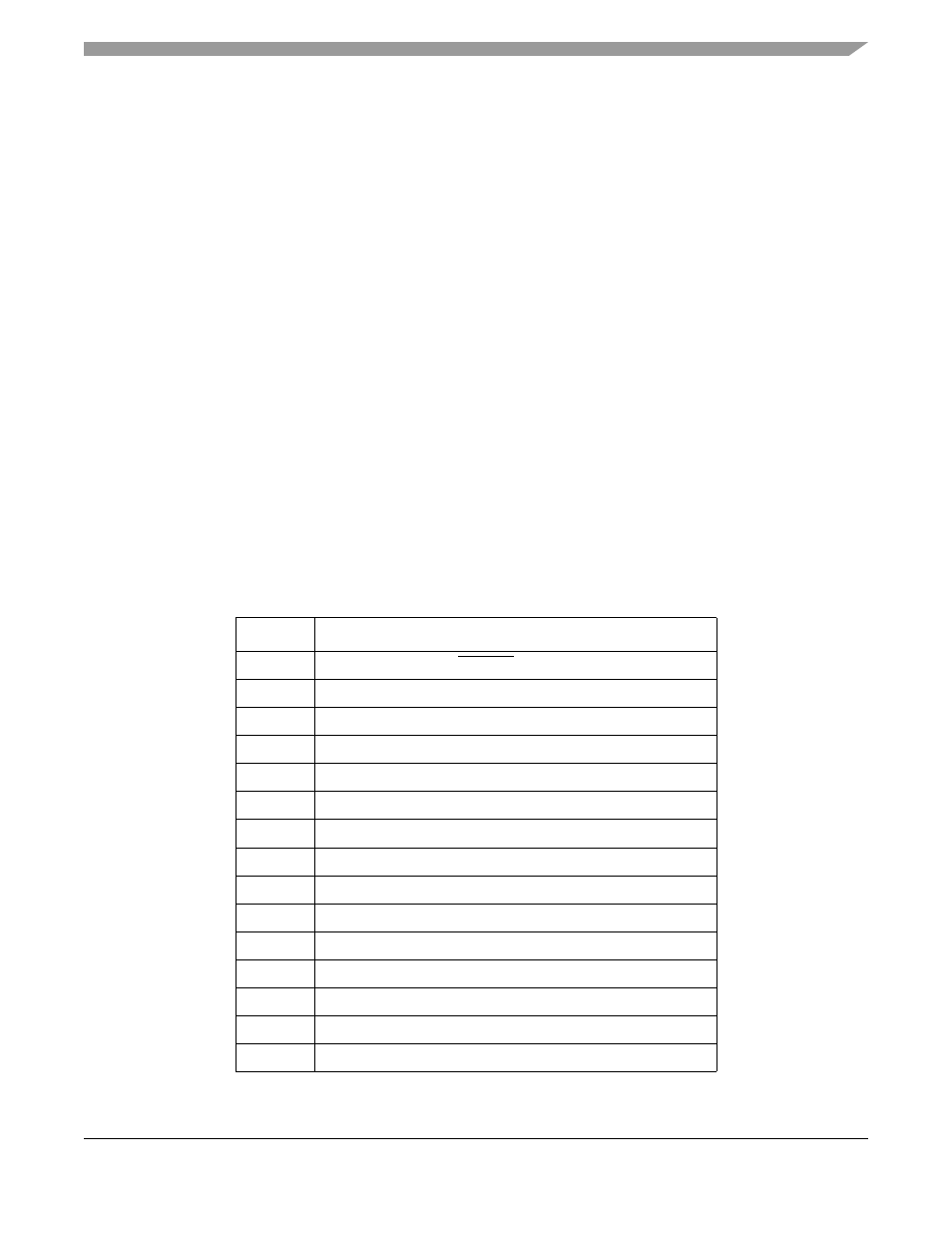

Table 14-2. Peripheral Prioritization

Priority

Request

1

Reset in the CPCR or SRESET

2

SDMA bus error

3

Commands issued to the CPCR

4

IDMA[1–4] emulation (default—option 1)

1

5

Emergency (from FCCs, MCCs, and SCCs)

6

IDMA[1–4] emulation (option 2)

1

7

FCC1 receive

8

FCC1 transmit

9

MCC1 receive

2

10

MCC2 receive

11

MCC1 transmit

2

12

MCC2 transmit

13

FCC2 receive

14

FCC2 transmit

15

FCC3 receive