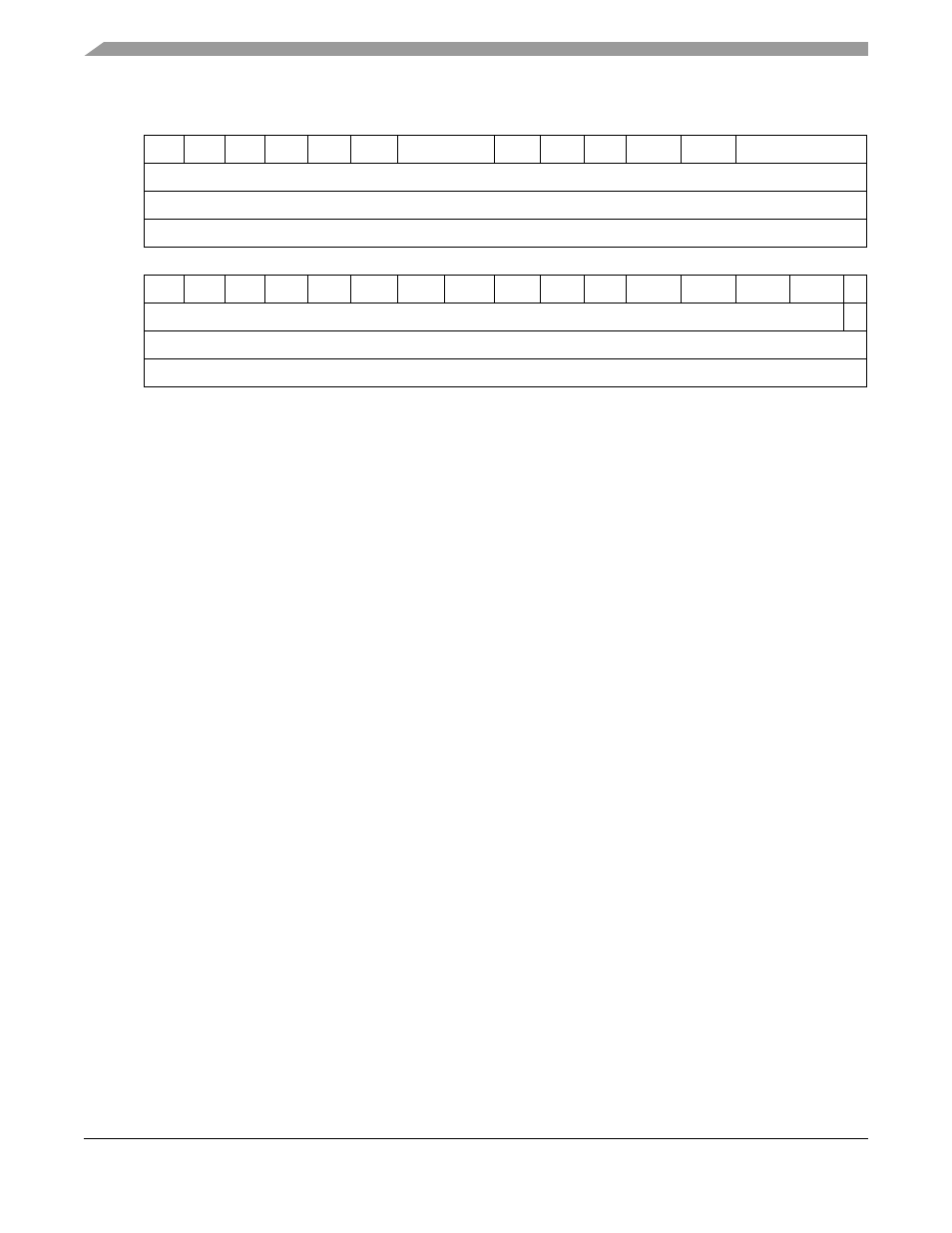

Figure 4-15. sipnr_l, 5 siu interrupt mask registers (simr_h and simr_l), Sipnr_l -22 – Freescale Semiconductor MPC8260 User Manual

Page 194: Figure 4-15

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-22

Freescale Semiconductor

When a pending interrupt is handled, the user clears the corresponding SIPNR bit. However, if an event

register exists, the unmasked event register bits should be cleared instead, causing the SIPNR bit to be

cleared.

SIPNR bits are cleared by writing ones to them. Because the user can only clear bits in this register, writing

zeros to this register has no effect.

Note that the SCC/FCC/MCC SIPNR bit positions are not changed according to their relative priority.

4.3.1.5

SIU Interrupt Mask Registers (SIMR_H and SIMR_L)

Each bit in the SIU interrupt mask register (SIMR) corresponds to a interrupt source. The user masks an

interrupt by clearing and enables an interrupt by setting the corresponding SIMR bit. When a masked

interrupt occurs, the corresponding SIPNR bit is set, regardless of the SIMR bit although no interrupt

request is passed to the core.

If an interrupt source requests interrupt service when the user clears its SIMR bit, the request stops. If the

user sets the SIMR bit later, a previously pending interrupt request is processed by the core, according to

its assigned priority. The SIMR can be read by the user at any time.

shows the SIMR_H register.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

15

Field FCC1 FCC2 FCC3

—

MCC1 MCC2

—

SCC1 SCC2 SCC3 SCC4

TC

2

—

Reset

0000_0000_0000_0000

1

R/W

R/W

Addr

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field I2C

SPI

RTT SMC1 SMC2 IDMA1 IDMA2 IDMA3 IDMA4 SDMA

—

TIMER1 TIMER2 TIMER3 TIMER4 —

Reset

0000_0000_0000_000

1

0

1

R/W

R/W

Addr

0x10C0E

1

These fields are zero after reset because their corresponding mask register bits are cleared (disabled).

2

MPC8264 and MPC8266 only. Reserved on all other devices.

Figure 4-15. SIPNR_L