Freescale Semiconductor MPC8260 User Manual

Page 200

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-28

Freescale Semiconductor

11

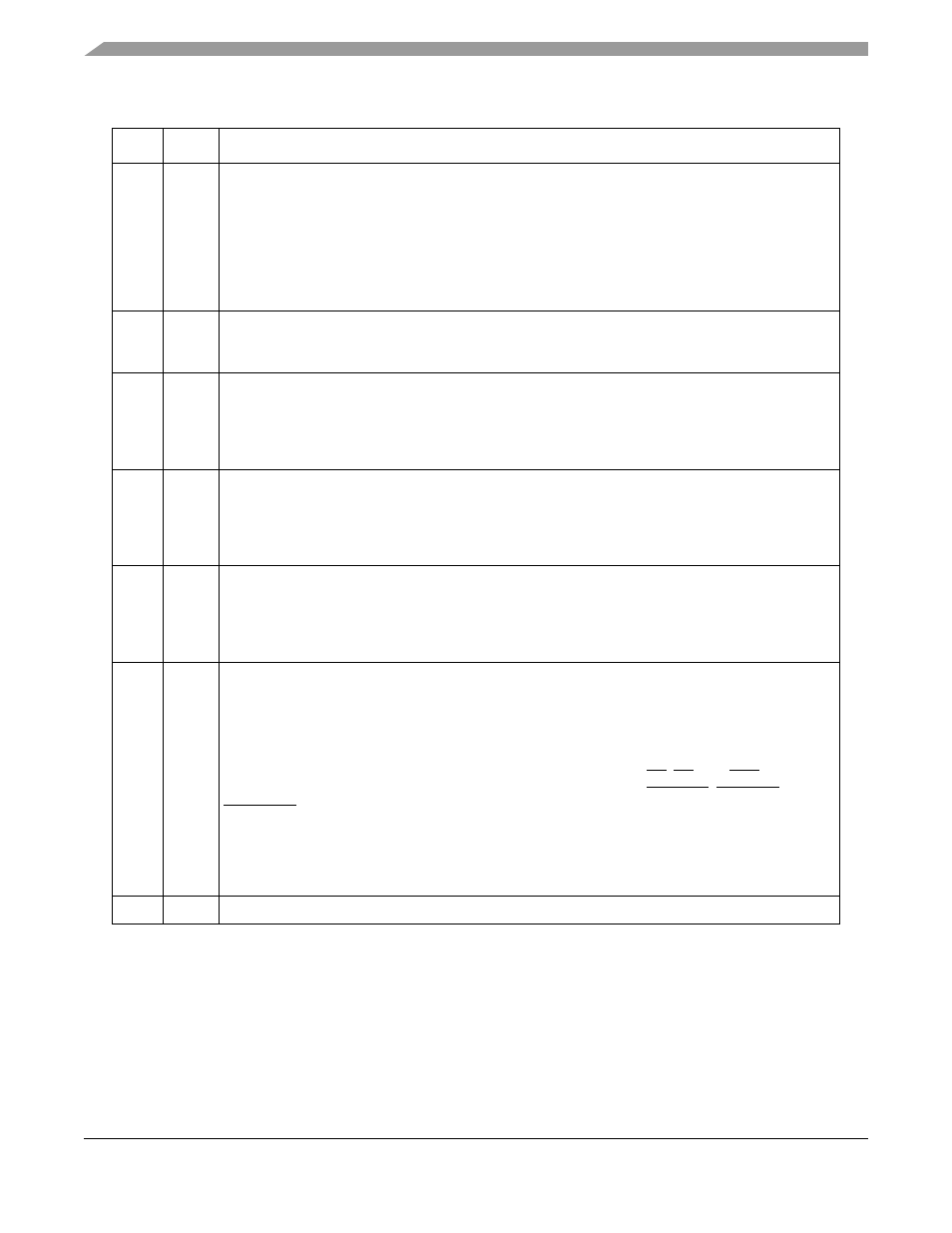

EAV

Enable address visibility. Normally, when the PowerQUICC II is in single-PowerQUICC II bus mode,

the bank select signals for SDRAM accesses are multiplexed on the 60x bus address lines. So, for

SDRAM accesses, the internal address is not visible for debug purposes. However the bank select

signals can also be driven on dedicated pins (see SIUMCR[APPC]). In this case EAV can be used to

force address visibility.

0 Bank select signals are driven on 60x bus address lines. There is no full address visibility.

1 Bank select signals are not driven on address bus. During READ and WRITE commands to

SDRAM devices, the full address is driven on 60x bus address lines.

12

ETM

Compatibility mode enable. See

Section 8.4.3.8, “Extended Transfer Mode.”

0 Strict 60x bus mode. Extended transfer mode is disabled.

1 Extended transfer mode is enabled.

13

LETM

Local bus compatibility mode enable. See

Section 8.4.3.8, “Extended Transfer Mode.”

0 Extended transfer mode is disabled on the local bus.

1 Extended transfer mode is enable on the local bus.

Note that if the local bus memory controller is configured to work with read-modify-write parity, LETM

must be cleared.

14

EPAR

Even parity. Determines odd or even parity on the 60x bus.

0 Odd parity

1 Even parity

Writing the memory with EPAR = 1 and reading the memory with EPAR = 0 generates parity errors

for testing.

15

LEPAR Local bus even parity. Determines odd or even parity on the local bus.

0 Odd parity

1 Even parity

Writing the memory with LEPAR = 1 and reading the memory with LEPAR = 0 generates parity errors

for testing.

16–18

NPQM Non PowerQUICC II master. Identifies the type of bus masters which are connected to the arbitration

lines when the PowerQUICC II is in internal arbiter mode. Possible types are PowerQUICC II master

and non-PowerQUICC II master. This field is related to the data pipelining bits (BRx[DR]) in the

memory controller. Because an external bus master that is not a PowerQUICC II cannot use the data

pipelining feature, the PowerQUICC II, which controls the memory, needs to know when a

non-PowerQUICC II master is accessing the memory and handle the transaction differently.

NPQM[0] designates the type of master connected to the set of pins BR, BG, and DBG.

NPQM[1] designates the type of master connected to the set of pins EXT_BR2, EXT_BG2, and

EXT_DBG2.

NPQM[2] designates the type of master which is connected to the set of pins EXT_BR3, EXT_BG3

and EXT_DBG3

0 The bus master connected to the arbitration lines is a PowerQUICC II.

1 The bus master connected to the arbitration lines is not a PowerQUICC II.

19–20

—

Reserved, should be cleared.

Table 4-9. BCR Field Descriptions (continued)

Bits

Name

Description