Table 19-5. dcm field descriptions (continued), Dcm field descriptions -20, Table 19-5 – Freescale Semiconductor MPC8260 User Manual

Page 664

SDMA Channels and IDMA Emulation

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

19-20

Freescale Semiconductor

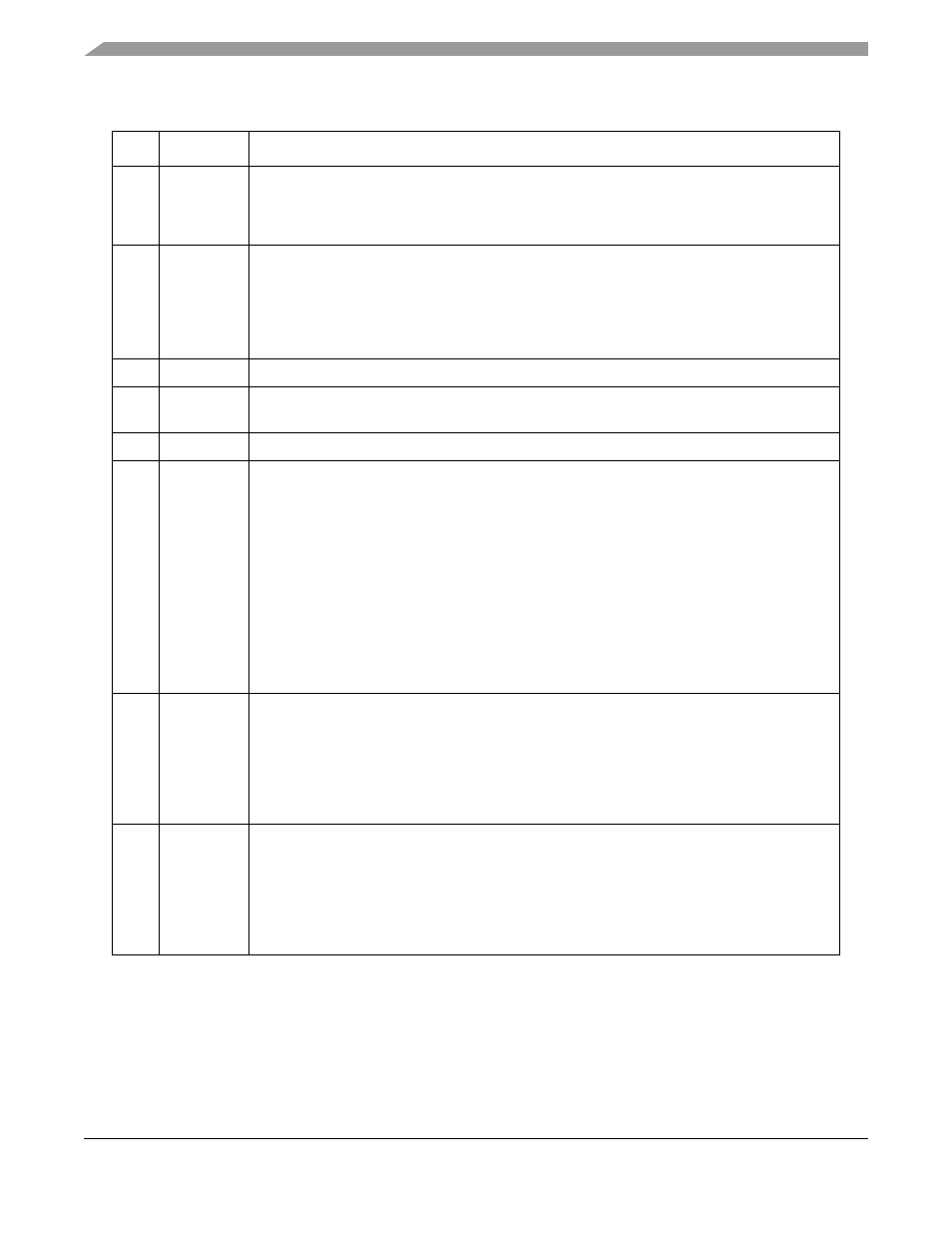

Table 19-5. DCM Field Descriptions

Bits

Name

Description

0

FB

Fly-by mode. See Table 19-6..

0 Dual-address mode.

1 Fly-by (single-address) mode. The internal IDMA transfer buffer is not used. Valid only in

peripheral-to-memory (S/D=10) or memory-to-peripheral (S/D=01) modes.

1

LP

Low priority. Applies to memory-to-memory accesses only. See

Configuration and Protection Registers

.”

0 The IDMA transaction to memory is in middle CPM request priority.

1 The IDMA transaction to memory is in low CPM request priority.

Note that IDMA single-address (fly-by) transfers with external peripherals are always high

priority, ignoring this bit and bypassing other pending SDMA requests.

2–4

—

Reserved, should be cleared.

5

TC2

Driven on TC[2] during IDMA transactions. The TC[0–1] signals are always driven to 0b11

during IDMA transactions.

6

—

Reserved, should be cleared.

7–9

DMA_WRA

P

DMA wrap. Defines the size of the IDMA transfer buffer. The IDMA pointer wraps to the

beginning of the buffer whenever DMA_WRAP bytes have been transferred to/from the buffer.

000 64 byte

001 128 byte

010 256 byte

011 512 byte

100 1024 byte

101 2048 byte

11x Reserved

describes the relations between the parameter’s initial value and

SS_MAX, STS, DTD and DCM[S/D] parameters.

The IDMA transfer buffer (DPR_BUF) size should be consistent with DCM[DMA_WRAP]; that is

DPR_BUF = 64 X 2

(DMA_WRAP)

.

10

SINC

Source increment address.

0 Source address pointer (S_PTR) is not incremented in the source read transaction. Should

be cleared for peripheral-to-memory transfers if the peripheral has a fixed address.

1 CP increments the source address pointer (S_PTR) with the number of bytes transferred in

the source read transaction. Used for memory-to-memory and memory-to-peripheral

transfers.

In fly-by mode, SINC controls the memory address increment and should equal DINC.

11

DINC

Destination increment address.

0 Destination address pointer (D_PTR) is not changed in the destination write transaction.

Used for memory-to-peripheral transfers if the peripheral has a fixed address.

1 CP increments the destination pointer (D_PTR) with the number of bytes transferred in the

destination write transaction. Used for memory-to-memory and memory-to-peripheral

transfers.

In fly-by mode, DINC should equal SINC.