Freescale Semiconductor MPC8260 User Manual

Page 245

External Signals

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

6-5

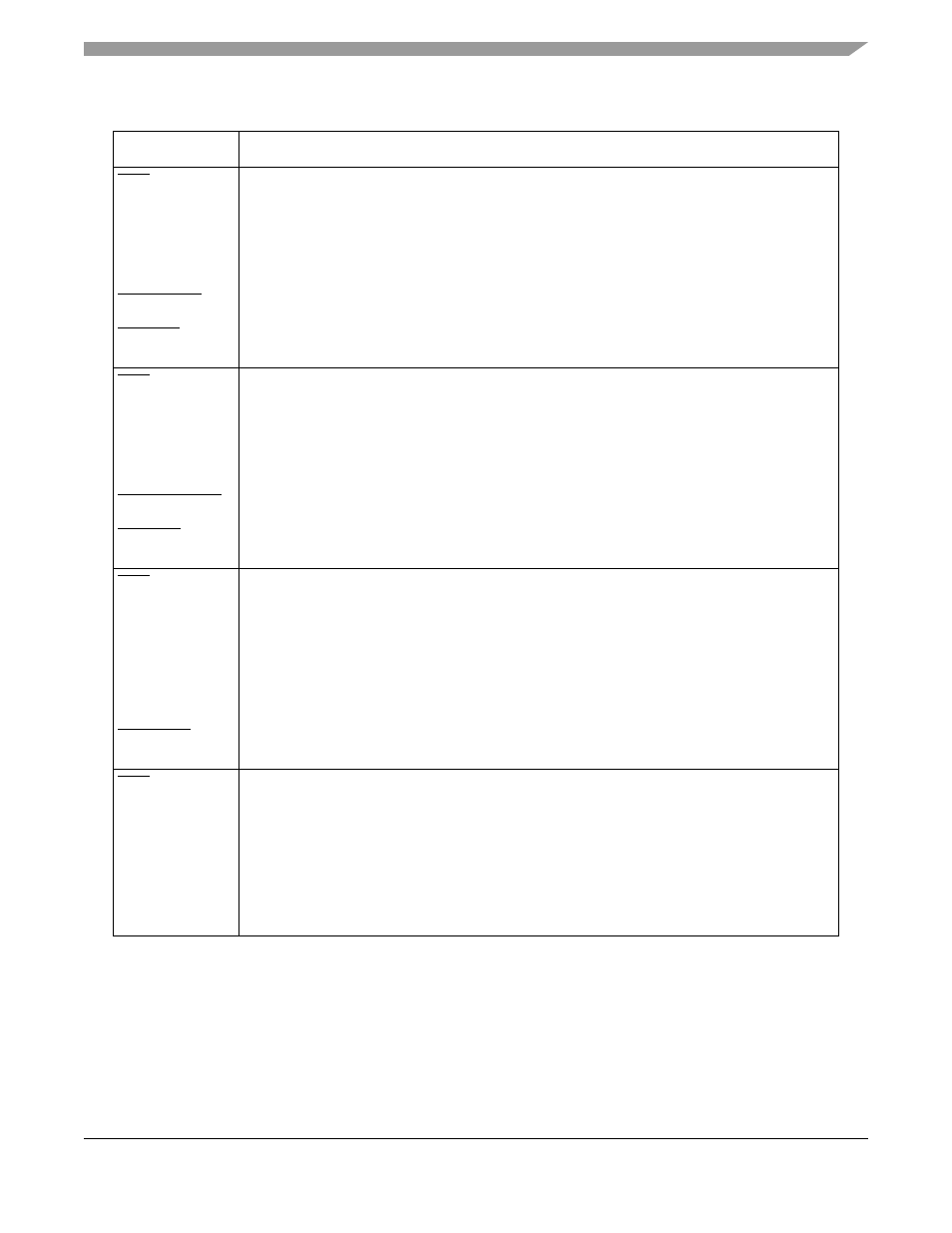

IRQ3

DP[3]

CKSTP_OUT

EXT_BR3

Interrupt request 3—This input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 3—(Input/output) The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 3 pin should give odd parity (odd number of 1’s) on the

group of signals that includes data parity 3 and D[24–31].

Checkstop output—(Output) Assertion indicates that the core is in its checkstop mode.

External bus request 3—(Input) An external master should assert this pin to request 60x bus

ownership from the internal arbiter.

IRQ4

DP[4]

CORE_SRESET

EXT_BG3

Interrupt request 4—This input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 4—(Input/output) The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 4 pin should give odd parity (odd number of ‘1’s) on the

group of signals that includes data parity 4 and D[32–39].

Core system reset—(Input) Asserting this pin will force the core to branch to its reset vector.

External bus grant 3—(Output) The PowerQUICC II asserts this pin to grant 60x bus ownership

to an external bus master.

IRQ5

DP[5]

TBEN

EXT_DBG3

Interrupt request 5—This input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 5—(Input/output) The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 5 pin should give odd parity (odd number of ‘1’s) on the

group of signals that includes data parity 5 and D[40–47].

Time base enable—This is a count enable input to the Time Base counter in the core.

External data bus grant 3—(Output) The PowerQUICC II asserts this pin to grant 60x data bus

ownership to an external bus master.

IRQ6

DP[6]

CSE[0]

Interrupt request 6—This input is one of the eight external lines that can request (by means of the

internal interrupt controller) a service routine from the core.

60x data parity 6—(Input/output) The 60x agent that drives the data bus drives also the data parity

signals. The value driven on data parity 6 pin should give odd parity (odd number of ‘1’s) on the

group of signals that includes data parity 6 and D[48–55].

Cache set entry 0—The cache set entry outputs from the core represent the cache replacement

set element for the current core transaction reloading into or writing out of the cache.

Table 6-1. External Signals (continued)

Signal Description