6 extended hold time on read accesses, Table 11-32. trlx and ehtr combinations, Extended hold time on read accesses -59 – Freescale Semiconductor MPC8260 User Manual

Page 477: Trlx and ehtr combinations -59

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-59

11.5.1.6

Extended Hold Time on Read Accesses

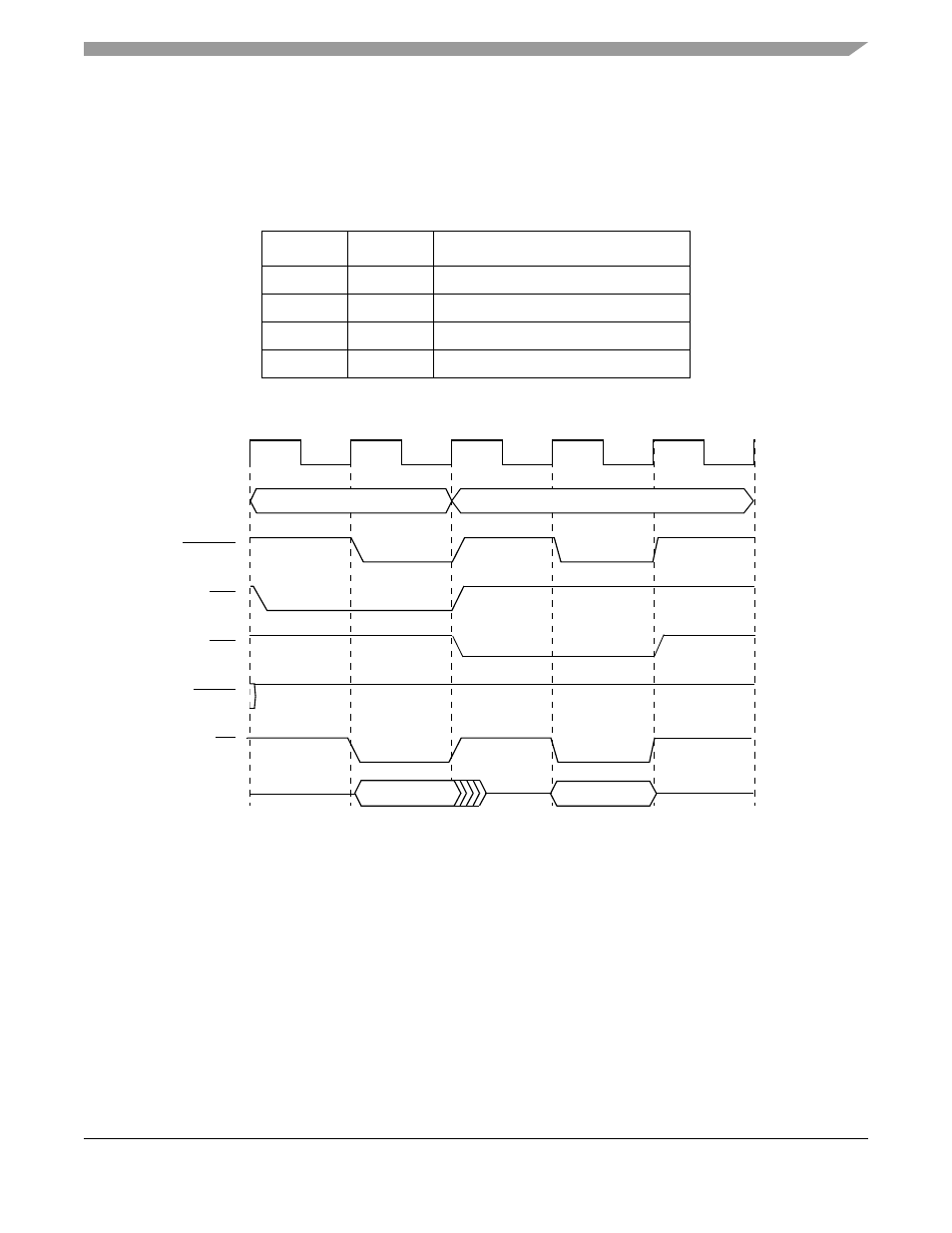

Slow memory devices that take a long time to turn off their data bus drivers on read accesses should choose

some combination of ORx[29–30] (TRLX and EHTR). Any access following a read access to the slower

memory bank is delayed by the number of clock cycles specified by

.

See

through

for timing examples.

Figure 11-50. GPCM Read Followed by Read (OR

x[29–30] = 00, Fastest Timing)

Table 11-32. TRLX and EHTR Combinations

ORx[TRLX] ORx[EHTR]

Number of Hold Time Clock Cycles

0

0

0

0

1

1

1

0

4

1

1

8

Clock

Address

PSDVAL

CSx

CSy

BCTL

x

OE

Data