Freescale Semiconductor MPC8260 User Manual

Page 251

External Signals

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

6-11

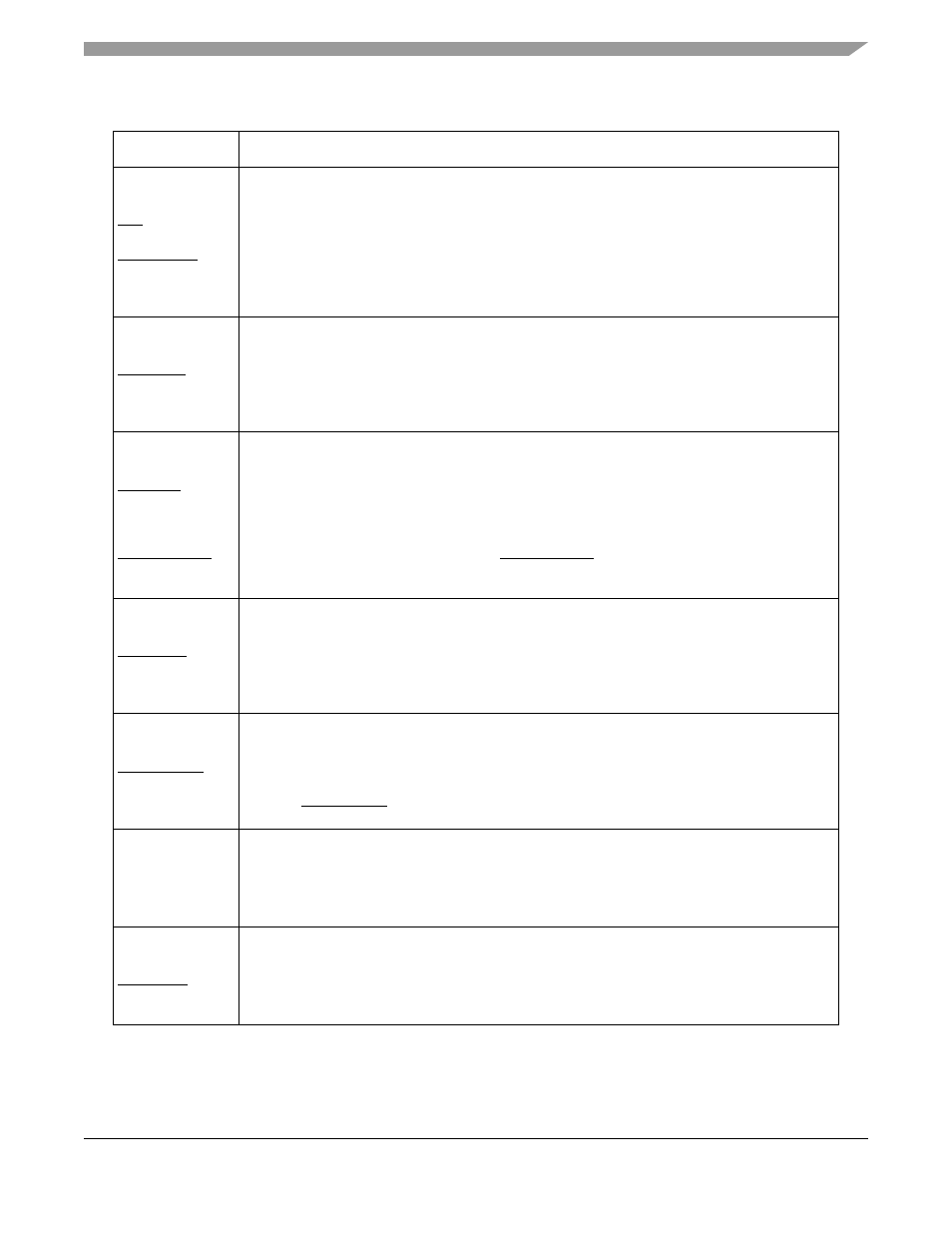

L_A15

SMI

PCI_FRAME

1

Local bus address 15—Local bus address bit 15 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

System management interrupt—System management interrupt input to the core.

PCI frame—PCI cycle frame input

/

output pin. Used by the current PCI master to indicate the

beginning and duration of an access. Driven by the PowerQUICC II when its PCI interface is the

master of the access. Otherwise, it is an input.

L_A16

PCI_TRDY

1

Local bus address 16—Local bus address bit 16 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI target ready—PCI target ready input/output pin. This pin is driven by the PowerQUICC II

when its PCI interface is the target of a PCI transfer. Assertion of this pin indicates that the PCI

target is ready to send or accept a data beat.

L_A17

PCI_IRDY

1

CKSTOP_OUT

Local bus address 17—Local bus address bit 17 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI initiator ready—PCI initiator ready input/output pin. This pin is driven by the PowerQUICC II

when its PCI interface is the initiator of a PCI transfer. Assertion of this pin indicates that the PCI

initiator is ready to send or accept a data beat.

Checkstop output—(Output) Assertion of CKSTOP_OUT indicates the core is in checkstop

mode.

L_A18

PCI_STOP

1

Local bus address 18—Local bus address bit 18 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI stop—PCI stop input/output pin. This pin is driven by the PowerQUICC II when its PCI

interface is the target of a PCI transfer. Assertion of this pin indicates that the PCI target is

requesting the master to stop the current PCI transfer.

L_A19

PCI_DEVSEL

1

Local bus address 19—Local bus address bit 19 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI device select—PCI device select input/output pin. This pin is driven by the PowerQUICC II

when its PCI interface has decoded its own address as the target of the current PCI transfer. As

an input, PCI_DEVSEL indicates whether any device on the PCI bus has been selected.

L_A20

PCI_IDSEL

1

Local bus address 20—Local bus address bit 20 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI initialization device select—(Input) Used to select the PowerQUICC II’s PCI interface during

a PCI configuration cycle.

L_A21

PCI_PERR

1

Local bus address 21—Local bus address bit 21 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI parity error—PCI data parity error input/output pin. Assertion of this pin indicates that a data

parity error was detected during a PCI transfer (except for a special cycle).

Table 6-1. External Signals (continued)

Signal Description