1 fast ethernet on the powerquicc ii, Figure 35-2. ethernet block diagram, 2 features – Freescale Semiconductor MPC8260 User Manual

Page 1198: Fast ethernet on the powerquicc ii -2, Features -2, Ethernet block diagram -2

Fast Ethernet Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

35-2

Freescale Semiconductor

10-Mbps Ethernet basic timing specifications follow:

•

Transmits at 0.8 µs per byte

•

The preamble plus start frame delimiter is sent in 6.4 µs.

•

The minimum interframe gap is 9.6 µs.

•

The slot time is 51.2 µs.

100-Mbps Ethernet basic timing specifications follow:

•

Transmits at 0.08 µs per byte

•

The preamble plus start frame delimiter is sent in 0.64 µs.

•

The minimum interframe gap is 0.96 µs.

•

The slot time is 5.12 µs.

35.1

Fast Ethernet on the PowerQUICC II

When a general FCC mode register (GFMRx[MODE]) selects Ethernet protocol, that FCC performs the

full set of IEEE 802.3/Ethernet CSMA/CD media access control (MAC) and channel interface functions.

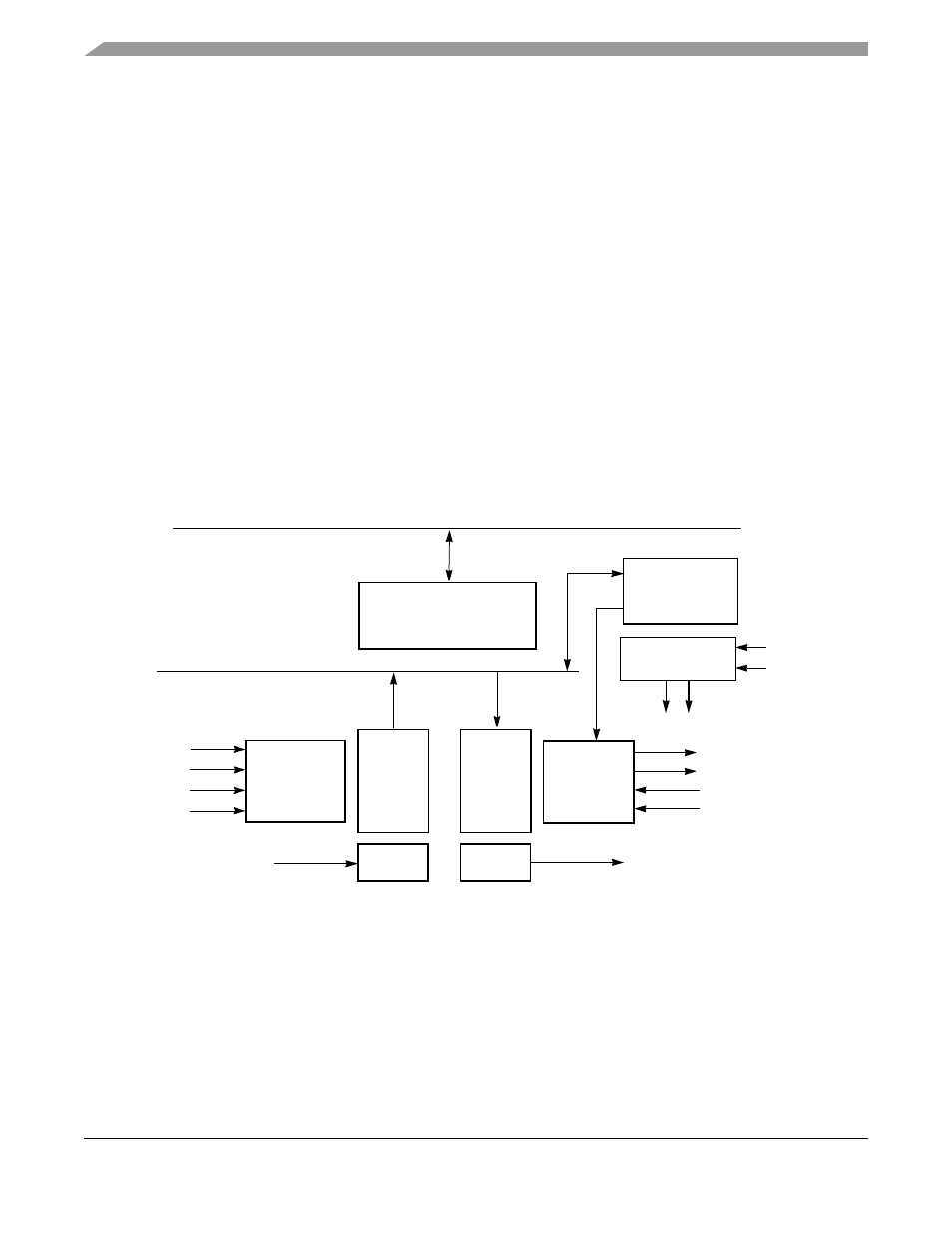

shows a block diagram of the FCC Ethernet control logic.

Figure 35-2. Ethernet Block Diagram

35.2

Features

The following is a list of Fast Ethernet key features:

•

Support for Fast Ethernet through the MII (media-independent interface)

•

Performs MAC (media access control) layer functions of Fast Ethernet and IEEE 802.3x

Shifter

Receive

Receiver

Control

UNIT

FIFO

Shifter

Transmit

Transmitter

Control

Unit

FIFO

Slot Time

Clock

Generator

Internal Clocks

Control

Registers

TXD[3–0]

RXD[3–0]

Peripheral Bus

60x-Bus

Data

Data

RX_CLK

TX_CLK

And Defer

Counter

TX_ER

Random

No

.

CRS

CRS

COL

RX_ER

TX_EN

COL

RX_DV