Freescale Semiconductor MPC8260 User Manual

Page 1305

Reference Manual (Rev 1) Errata

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

B-3

PCI controller can initiate global transactions—Assertion must occur at least one

clock cycle following AACK for the current transaction and at least one clock

cycle after ARTRY can be asserted.

8.4.4.1. 8-24

Replace the third sentence of the paragraph that follows Figure 8-7 with the

following (changes appear in boldface):

If the assertion of ARTRY is received up to or on the bus cycle as the first (or only)

assertion of TA for the data tenure, the PowerQUICC II ignores the first data beat.

8.4.4.1. 8-24

Replace the first sentence of the paragraph that begins, “Note that the system...”

with the following:

Note that the system must ensure that ARTRY is never asserted later than the cycle

of the first or only assertion of TA. (If the PCI controller can initiate global

transactions, the system must ensure that ARTRY is never asserted on the same

cycle or later then the first or only assertion of TA.)

9.11, 9-30

Replace the second paragraph with the following:

Both the PCI configuration and memory-mapped internal registers of the PCI

bridge are intrinsically little endian and are described using classic bit-numbering;

that is, the lowest memory address contains the least-significant byte of the

register, and bit 0 is the least-significant bit of the register.

9.11.1.11, 9-42

The second sentence should read as follows (changes appear in boldface):

The IOU asserts an interrupt or machine check only if the mask bit for the error

condition (refer to Table 9-14) is set.

9.11.1.14, 9-45

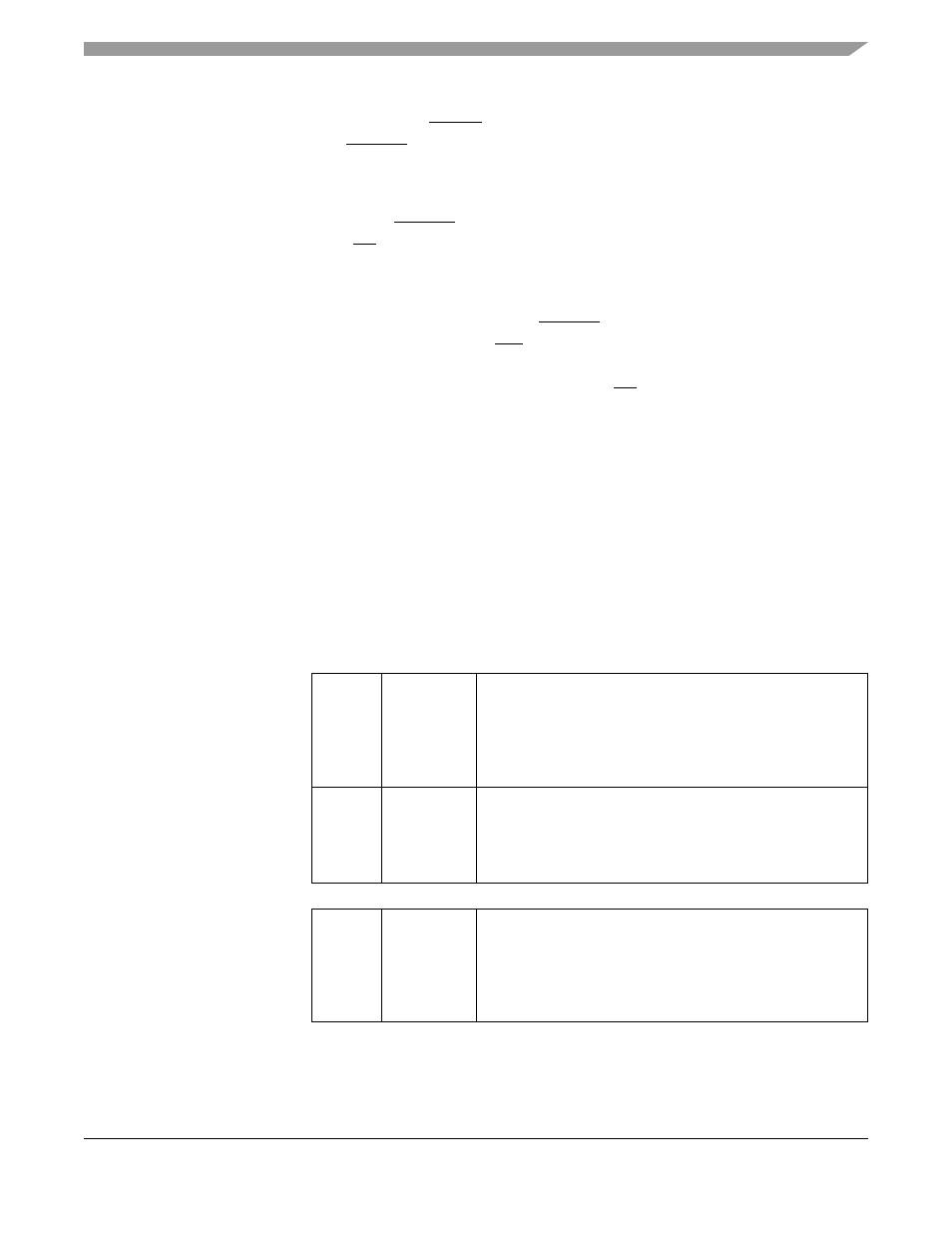

In Table 9-15, the descriptions of Transaction size, Error source, and Valid

information should appear as follows (changes or additions appear in boldface):

21–20

Transaction

size

This is the size of the transaction in doublewords (4 bytes) (the

PCI bridge as master only)

00 4 doublewords

01 1 doubleword

10 2 doublewords

11 3 doublewords

19–16

Error source

The source of the PCI transaction.

0000 External master

0001 60x master

0101 DMA

All others are reserved.

0

Valid info

When this bit is set, the PCI bus error capture registers

(PCI_EACR, PCI_EDCR, and PCI_ECCR) contain valid

information.

Writing ‘0’ to this bit enables the capture of a new error in

the PCI bus error capture registers (PCI_EACR,

PCI_EDCR, and PCI_ECCR).