Freescale Semiconductor MPC8260 User Manual

Page 1130

Inverse Multiplexing for ATM (IMA)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

33-28

Freescale Semiconductor

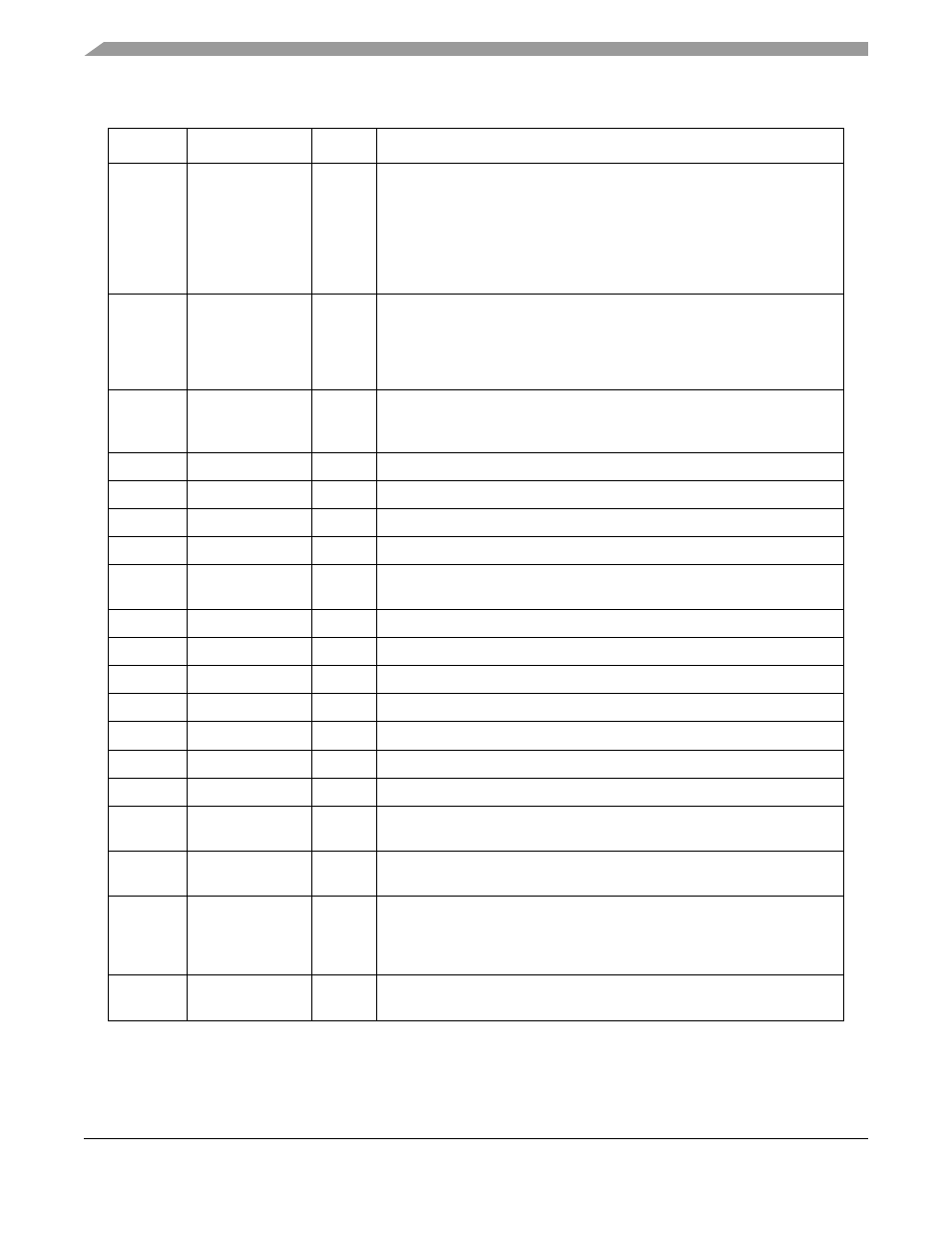

0x3C

TXPHYEN

Word

Transmit PHY enable. Bit array addressed by PHY address (e.g. bit 0

corresponds to PHY 0). Setting a bit enables transmission for the

corresponding PHY. Must be used to enable/disable the corresponding

PHY regardless of whether or not the PHY is defined as IMA in IMAPHY.

Only idle/unassigned cells are transmitted on disabled PHYs. Note that the

FCC must also be enabled in GFMR[ENT] for transmission to occur.

Bit 31 is reserved, and must be programmed to zero.

0x40

IMAPHY

Word

Bit array addressed by PHY address (e.g. bit 0 corresponds to PHY 0).

Setting a bit defines the corresponding PHY to operate in IMA mode.

Clearing a bit defines the corresponding PHY to operate as a normal

(non-IMA) multi-PHY.

Bit 31 is reserved, and must be programmed to zero.

0x44

IMAEXTBASE

Word

IMA external structure base pointer. Points to region in external memory

where external IMA data structures are located. Must be aligned to a 1MB

boundary (i.e. program bits 12-31 to zero).

0x48

IMAGRPT_TX

Hword

Offset of IMA group transmit table in DPRAM. Must be 16-byte aligned.

0x4A

IMAGRPT_RX

Hword

Offset of IMA group receive table in DPRAM. Must be 64-byte aligned.

0x4C

IMALINKT_TX

Hword

Offset of IMA link transmit table in DPRAM. Must be 32-byte aligned.

0x4E

IMALINKT_RX

Hword

Offset of IMA link receive table in DPRAM. Must be 32-byte aligned.

0x50

IRLINKSTAT

Hword

Offset of the optional IMA link receive statistics table in DPRAM. Must be

8-byte aligned.

0x52

TMP_LPTR_RX

Hword

Microcode-managed parameter. Temporary storage of link table pointer.

0x54

TMP_LPTR_TX

Hword

Microcode-managed parameter. Temporary transmit table pointer.

0x56

TMP_GPTR_TX

Hword

Microcode-managed parameter. Temporary transmit group pointer.

0x58

TMP_GPORD_TX Hword

Microcode-managed parameter. Temporary transmit group order pointer.

0x5A

TMP_GPTR_RX

Hword

Microcode-managed parameter. Temporary receive group pointer.

0X5C

TMP_RTRN_RX

Hword

Microcode-managed parameter. Temporary return pointer.

0x5E

TMP_GPTR2_RX

Hword

Microcode-managed parameter. Temporary receive group pointer 2.

0x60–0x68 IDCR ROOT

PARAMETERS

—

Refer to

Section 33.4.8, “IDCR Timer Programming

,” for more details

0x68

—

—

Reserved. Must be programmed to zero during initialization.

0x6C

ITPGRPO

Hword

Required for optional TRL Service Latency enhancement only.

IMA Temp Group Order - Points to the base of a 2byte temp pointer storage

per group. Software initialized before FCC is enabled. Microcode managed

parameter.

0x6E–0x7

F

—

—

Reserved. Must be programmed to zero during initialization.

1

Boldfaced

entries in the above table indicate parameters which must be initialized by the user. All other parameters

are managed by the microcode and should be initialized to zero unless otherwise stated.

Table 33-3. IMA Root Table

1

(continued)

Offset Name

Width

Description