Table 23-8. transmit errors, Table 23-9. receive errors, 11 bisync mode register (psmr) – Freescale Semiconductor MPC8260 User Manual

Page 760: Bisync mode register (psmr) -10, Transmit errors -10, Receive errors -10, Section 23.11, “bisync mode register, Psmr), Table 23-8, Transmit errors

SCC BISYNC Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

23-10

Freescale Semiconductor

describes receive errors.

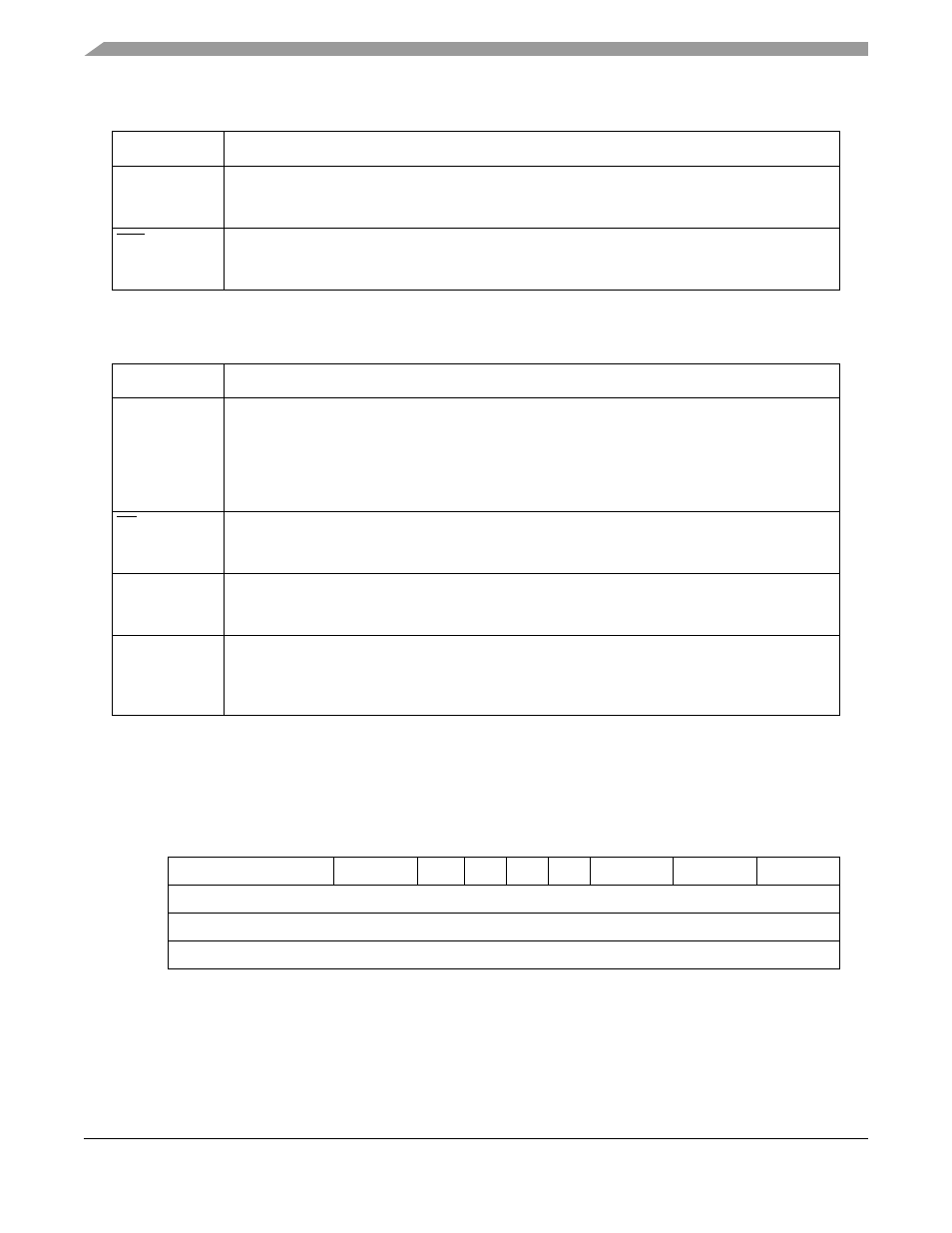

23.11 BISYNC Mode Register (PSMR)

The PSMR is used as the BISYNC mode register, shown in

. PSMR[RBCS, RTR, RPM, TPM]

can be modified on-the-fly.

describes PSMR fields.

Table 23-8.

Transmit Errors

Error

Description

Transmitter

Underrun

The channel stops sending the buffer, closes it, sets TxBD[UN], and generates aTXE interrupt if it

is enabled. The channel resumes transmission after a

RESTART

TRANSMIT

command is received.

Underrun cannot occur between frames or during a DLE–

XXX

pair in transparent mode.

CTS Lost during

Message

Transmission

The channel stops sending the buffer, closes it, sets TxBD[CT], and generates a TXE interrupt if not

masked. Transmission resumes when a

RESTART

TRANSMIT

command is received.

Table 23-9.

Receive Errors

Error

Description

Overrun

The controller maintains a receiver FIFO for receiving data. The CP begins programming the SDMA

channel (if the buffer is in external memory) and updating the CRC when the first byte is received in

the Rx FIFO. If an Rx FIFO overrun occurs, the controller writes the received byte over the previously

received byte. The previous character and its status bits are lost. The channel then closes the buffer,

sets RxBD[OV], and generates the RXB interrupt if it is enabled. Finally, the receiver enters hunt

mode.

CD Lost during

Message

Reception

The channel stops receiving, closes the buffer, sets RxBD[CD], and generates the RXB interrupt if

not masked. This error has the highest priority. If the rest of the message is lost, no other errors are

checked in the message. The receiver immediately enters hunt mode.

Parity

The channel writes the received character to the buffer and sets RxBD[PR]. The channel stops

receiving, closes the buffer, sets RxBD[PR], and generates the RXB interrupt if it is enabled. The

channel also increments PAREC and the receiver immediately enters hunt mode.

CRC

The channel updates the CR bit in the BD every time a character is received with a byte delay of

eight serial clocks between the status update and the CRC calculation. When control character

recognition is used to detect the end of the block and cause CRC checking, the channel closes the

buffer, sets the CR bit in the BD, and generates the RXB interrupt if it is enabled.

0

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

NOS

CRC

RBCS RTR

RVD

DRT

—

RPM

TPM

Reset

0

R/W

R/W

Addr

0x0x11A08 (PSMR1); 0x0x11A28 (PSMR2); 0x0x11A48 (PSMR3); 0x0x11A68 (PSMR4)

Figure 23-5. Protocol-Specific Mode Register for BISYNC (PSMR)