Figure 32-10. cps packet header format, 4 sssar tx queue descriptor, Figure 32-11. sssar tx queue descriptor – Freescale Semiconductor MPC8260 User Manual

Page 1079: Sssar tx queue descriptor -17, Cps packet header format -17, Section 32.3.5.4, “sssar tx queue descriptor, Figure 32-10

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

32-17

32.3.5.4

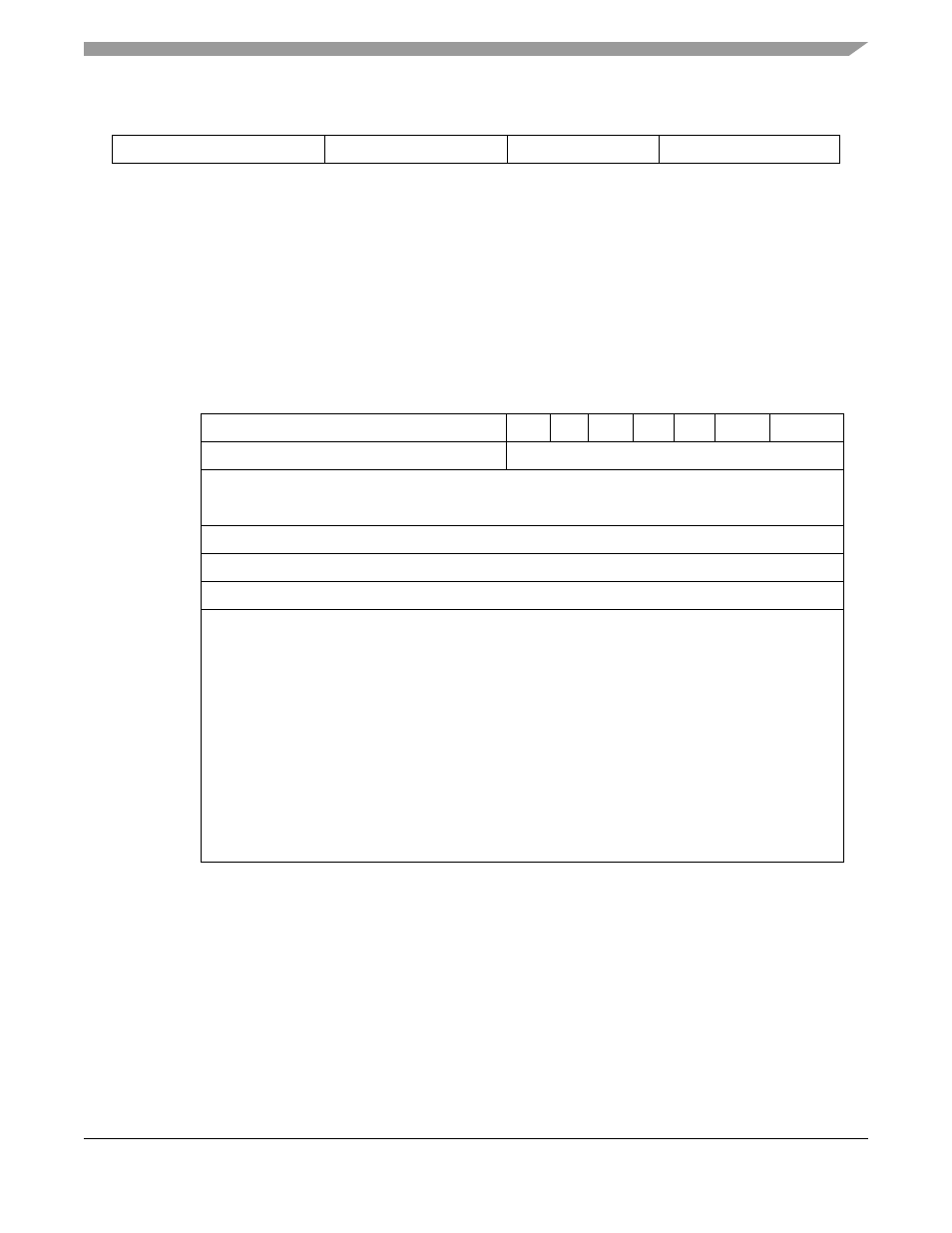

SSSAR Tx Queue Descriptor

A SSSAR TxBD table and its associated buffers are collectively called an SSSAR TX Queue. Each

SSSAR TX Queue is managed by an SSSAR TxQD, as shown in

. The TxQD contains the

base address of the BD table, the offset of the next BD to be serviced, the data buffer pointer, and other

queue-specific parameters. The NextQueue pointer is used to create a linked list of TxQDs, as described

in

Section 32.3.2, “Transmit Priority Mechanism.”

The SSSAR TxQD is located in the dual-port RAM in

a 32-byte aligned address.

describes the SSSAR TxQD fields.

0

7

8

13

14

18

19

23

Channel identifier (CID)

Length indicator (LI)

User-to-user ID (UUI)

Header error check (HEC)

Figure 32-10. CPS Packet Header Format

0

7

8

9

10

11

12

13

14

15

Offset + 0x00

—

BNM

UUI

INF

CPS TBM SSSAR

—

Offset + 0x02

Seg_Len

—

Offset + 0x04

TxBD Table Base

Offset + 0x06

Offset + 0x08

TxBD Table Offset Out

Offset + 0x0A

—

Offset + 0x0C

NextQueue

Offset + 0x0E

—

Offset + 0x10

Offset + 0x12

Offset + 0x14

Offset + 0x16

Offset + 0x18

Offset + 0x1a

Offset + 0x1C

Offset + 0x1E

Figure 32-11. SSSAR Tx Queue Descriptor