Table 2-5. exceptions and conditions (continued), Exceptions and conditions -22 – Freescale Semiconductor MPC8260 User Manual

Page 140

G2 Core

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

2-22

Freescale Semiconductor

exception is taken due to a trap or system call instruction, execution resumes at an address provided

by the handler.

•

Synchronous, imprecise—The PowerPC architecture defines two imprecise floating-point

exception modes, recoverable and nonrecoverable. These are not implemented on the

PowerQUICC II.

•

Asynchronous, maskable—The external, system management interrupt (SMI), and decrementer

interrupts are maskable asynchronous exceptions. When these exceptions occur, their handling is

postponed until the next instruction and any exceptions associated with that instruction complete

execution. If no instructions are in the execution units, the exception is taken immediately upon

determination of the correct restart address (for loading SRR0).

•

Asynchronous, nonmaskable—There are two nonmaskable asynchronous exceptions: system reset

and the machine check exception. These exceptions may not be recoverable, or may provide a

limited degree of recoverability. All exceptions report recoverability through MSR[RI].

2.5.2

PowerQUICC II Implementation-Specific Exception Model

As specified by the PowerPC architecture, all processor core exceptions can be described as either precise

or imprecise and either synchronous or asynchronous. Asynchronous exceptions (some of which are

maskable) are caused by events external to the processor’s execution. Synchronous exceptions, which are

all handled precisely by the processor core, are caused by instructions. The processor core exception

classes are shown in

Although exceptions have other characteristics as well, such as whether they are maskable or

nonmaskable, the distinctions shown in

define categories of exceptions that the processor core

handles uniquely. Note that

includes no synchronous imprecise instructions.

The processor core’s exceptions, and conditions that cause them, are listed in

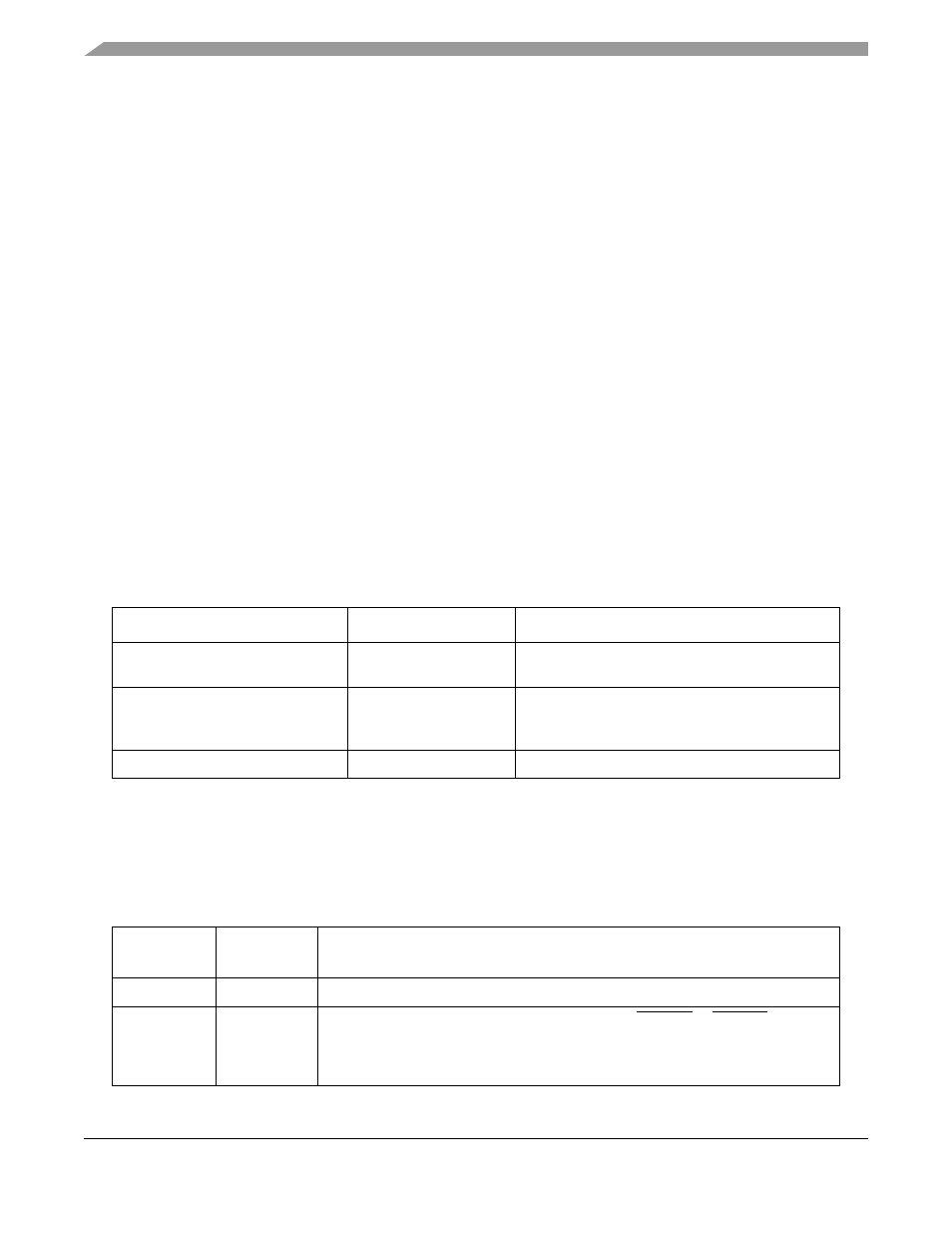

Table 2-4. Exception Classifications for the Processor Core

Synchronous/Asynchronous

Precise/Imprecise

Exception Type

Asynchronous, nonmaskable

Imprecise

Machine check

System reset

Asynchronous, maskable

Precise

External interrupt

Decrementer

System management interrupt

Synchronous

Precise

Instruction-caused exceptions

Table 2-5. Exceptions and Conditions

Exception

Type

Vector Offset

(hex)

Causing Conditions

Reserved 00000

—

System reset

00100

A system reset is caused by the assertion of either SRESET or HRESET. Note that

the reset value of the MSR exception prefix bit (MSR[IP]), described in the

G2 Core

Reference Manual

, is determined by the CIP bit in the hard reset configuration word.