Freescale Semiconductor MPC8260 User Manual

Page 86

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

lxxxiv

Freescale Semiconductor

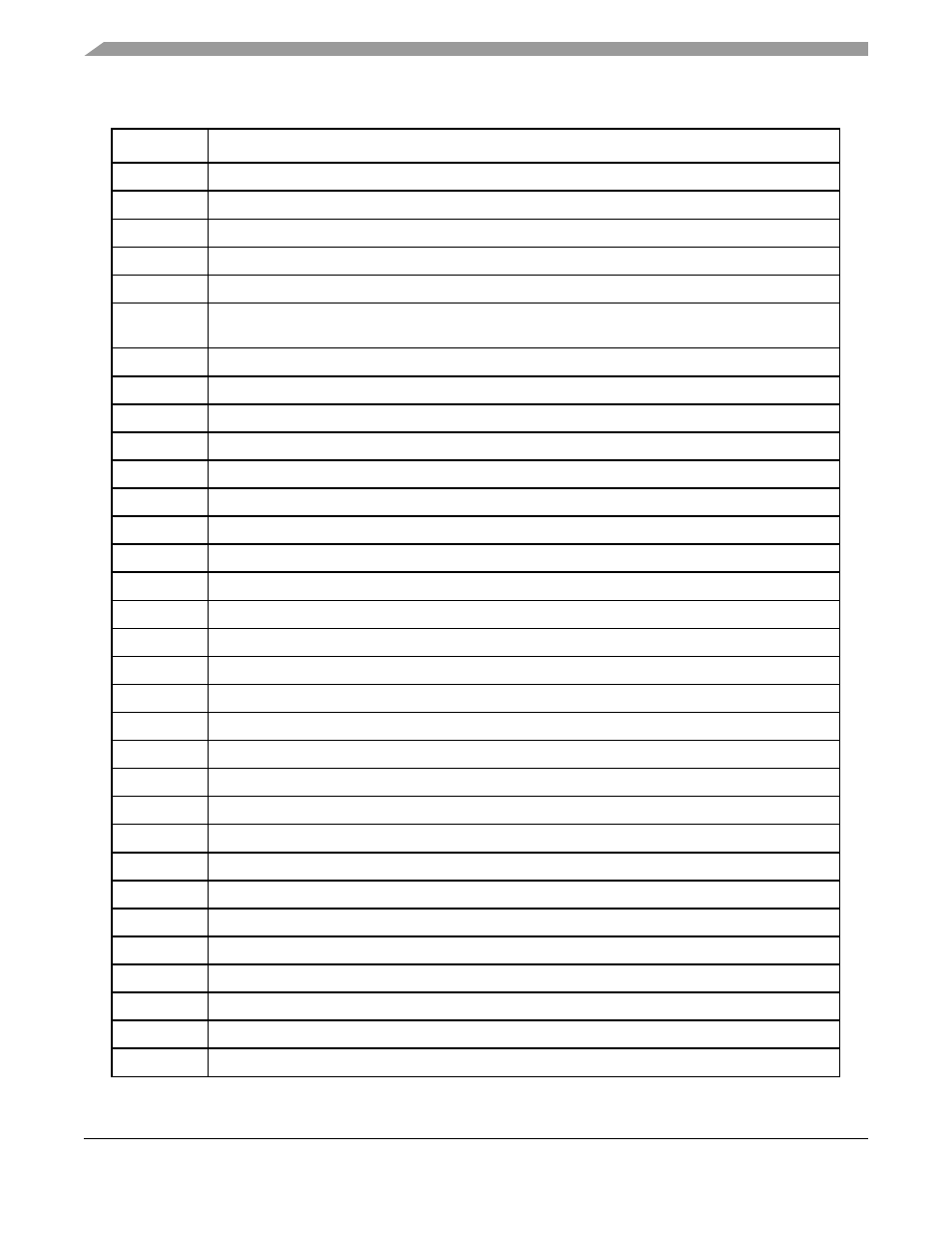

BIST

Built-in self test

BPU

Branch processing unit

BRI

Basic rate interface.

BUID

Bus unit ID

CAM

Content-addressable memory

CEPT

Conference des administrations Europeanes des Postes et Telecommunications (European

Conference of Postal and Telecommunications Administrations).

CMX

CPM multiplexing logic

CPM

Communication processor module

CR

Condition register

CRC

Cyclic redundancy check

CTR

Count register

DABR

Data address breakpoint register

DAR

Data address register

DEC

Decrementer register

DMA

Direct memory access

DPLL

Digital phase-locked loop

DRAM

Dynamic random access memory

DSISR

Register used for determining the source of a DSI exception

DTLB

Data translation lookaside buffer

EA

Effective address

EEST

Enhanced Ethernet serial transceiver

EPROM

Erasable programmable read-only memory

FPR

Floating-point register

FPSCR

Floating-point status and control register

FPU

Floating-point unit

GCI

General circuit interface

GPCM

General-purpose chip-select machine

GPR

General-purpose register

GUI

Graphical user interface

HDLC

High-level data link control

I

2

C

Inter-integrated circuit

IDL

Inter-chip digital link

Table iii. Acronyms and Abbreviated Terms (continued)

Term

Meaning