Figure 18-9. timer event registers (ter1-ter4), Table 18-4. ter field descriptions, Timer event registers (ter1–ter4) -8 – Freescale Semiconductor MPC8260 User Manual

Page 644: Ter field descriptions -8

Timers

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

18-8

Freescale Semiconductor

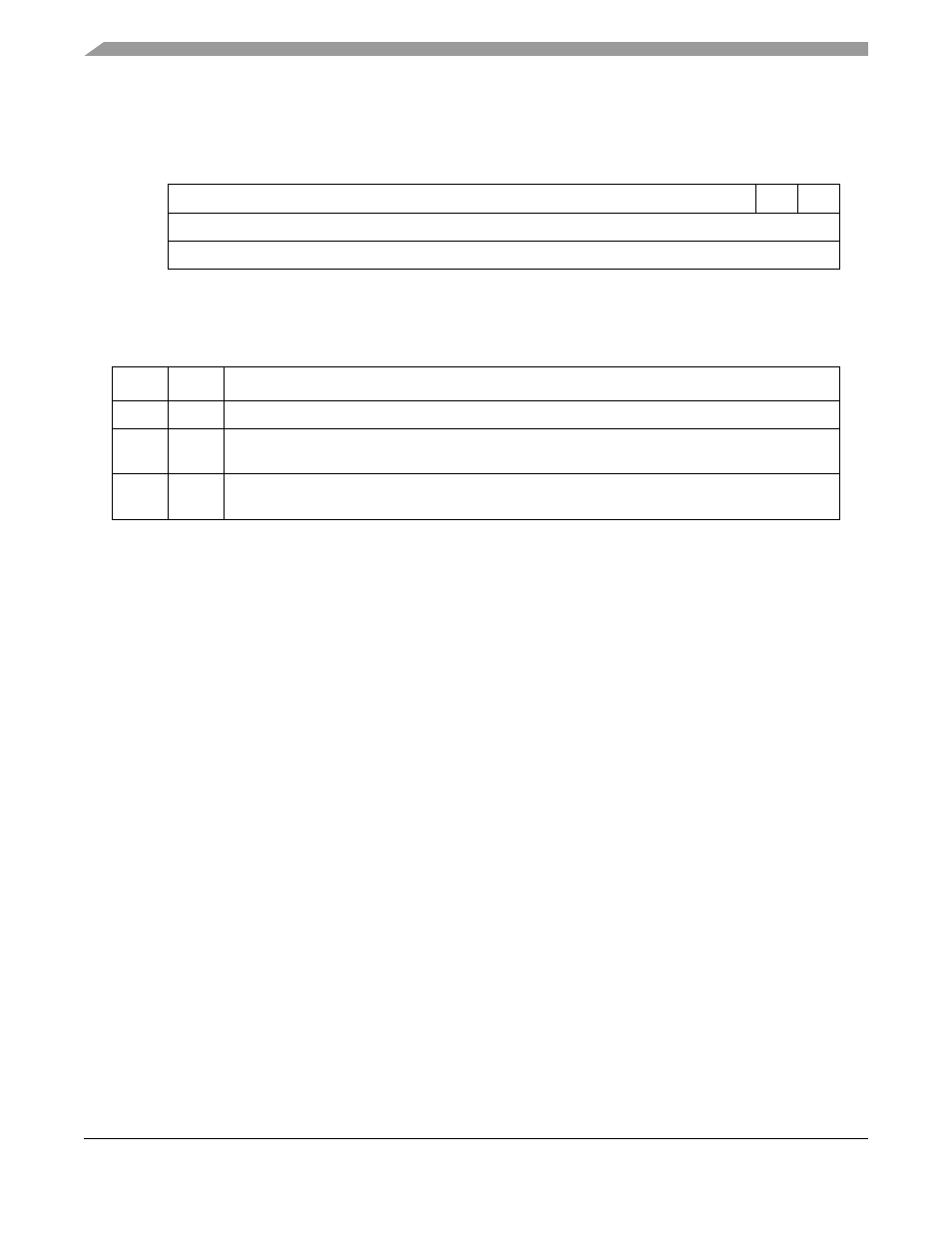

Writing ones clears event bits; writing zeros has no effect. Both event bits must be cleared before the timer

negates the interrupt.

describes TER fields.

0

13

14

15

Field

—

REF

CAP

Reset

0x0000

Addr

0x0x10DB0 (TER1); 0x0x10DB2 (TER2); 0x0x10DB4 (TER3); 0x0x10DB6 (TER4)

Figure 18-9. Timer Event Registers (TER1–TER4)

Table 18-4. TER Field Descriptions

Bits

Name

Description

0–13

–

Reserved, should be cleared.

14

REF

Output reference event. The counter has reached the TRR value. TMR[ORI] is used to enable the

interrupt request caused by this event.

15

CAP

Capture event. The counter value has been latched into the TCR. TMR[CE] is used to enable

generation of this event.