6 effect of port size on data transfers, Effect of port size on data transfers -16 – Freescale Semiconductor MPC8260 User Manual

Page 290

The 60x Bus

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

8-16

Freescale Semiconductor

8.4.3.6

Effect of Port Size on Data Transfers

The PowerQUICC II can transfer operands through its 64-bit data port. If the transfer is controlled by the

internal memory controller, the PowerQUICC II can support 8-, 16-, 32-, and 64-bit data port sizes as

demonstrated in

. The bus requires that the portion of the data bus used for a transfer to or from

a particular port size be fixed. A 64-bit port must reside on data bus bits D[0–63], a 32-bit port must reside

on bits D[0–31], a 16-bit port must reside on bits D[0–15], and an 8-bit port must reside on bits D[0–7].

The PowerQUICC II always tries to transfer the maximum amount of data on all bus cycles: for a word

operation, it always assumes the port is 64 bits wide when beginning the bus cycle; for burst and extended

byte cycles, a 64-bit bus is assumed.

Figure 8-6. shows the device connections on the data bus.

lists the bytes required on the data bus

for read cycles.

Misaligned—1st access

0 1 0

1 1 0

—

—

—

—

—

—

A

A

2nd access

0 1 0

0 0 0

A

A

—

—

—

—

—

—

Misaligned—1st access

0 0 1

1 1 1

—

—

—

—

—

—

—

A

2nd access

0 1 1

0 0 0

A

A

A

—

—

—

—

—

1

A: Byte lane used

2

—: Byte lane not used

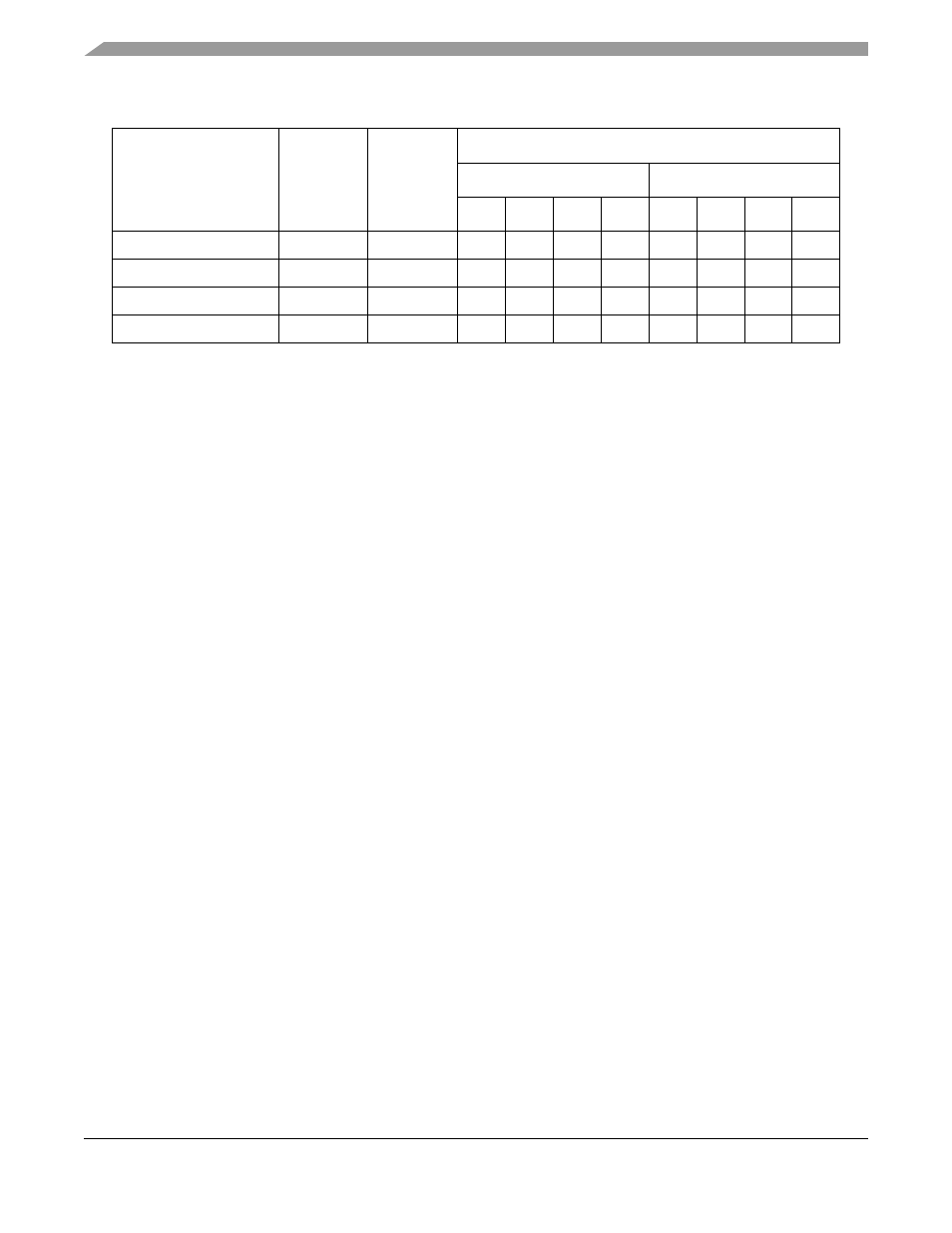

Table 8-7. Unaligned Data Transfer Example (4-Byte Example) (continued)

Program Size of

Word (4 bytes)

TSIZ[1–3]

A[29–31]

Data Bus Byte Lanes

D0...

...D31

D32...

...D63

B0

B1

B2

B3

B4

B5

B6

B7