2 transparent channel operation, 3 achieving synchronization in transparent mode, 1 in-line synchronization pattern – Freescale Semiconductor MPC8260 User Manual

Page 1244: Figure 37-1. in-line synchronization pattern, Transparent channel operation -2, Achieving synchronization in transparent mode -2, In-line synchronization pattern -2

FCC Transparent Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

37-2

Freescale Semiconductor

•

Reverse data mode

•

Another protocol can be performed on the FCC’s other half (transmitter or receiver) during

transparent mode

•

External BD table

37.2

Transparent Channel Operation

The transparent transmitter and receiver operates in the same way as the HDLC controller of the FCC (see

Chapter 36, “FCC HDLC Controller”

) except in the following ways:

1. The FPSMR does not affect the transparent controller, only the GFMR does.

2. In Table 36-1 on page 36-3, MFLR, HMASK, RFTHR, and RFCNT must be cleared for proper

operation of the transparent receiver.

3. Transmitter synchronization has to be achieved using CTS before the transmitter begins sending;

see

Section 37.3, “Achieving Synchronization in Transparent Mode.”

37.3

Achieving Synchronization in Transparent Mode

Once the FCC transmitter is enabled for transparent operation in the GFMR, the TxBD is prepared for the

FCC, and the transmit FIFO is preloaded by the SDMA channel, transmit synchronization must be

established before data can be sent.

Similarly, once the FCC receiver is enabled for transparent operation in the GFMR and the RxBD is made

empty for the FCC, receive synchronization must occur before data can be received. The synchronization

process gives the user bit-level control of when the transmission and reception begins. The methods for

this are as follows:

•

An in-line synchronization pattern

•

External synchronization signals

•

Automatic sync

37.3.1

In-Line Synchronization Pattern

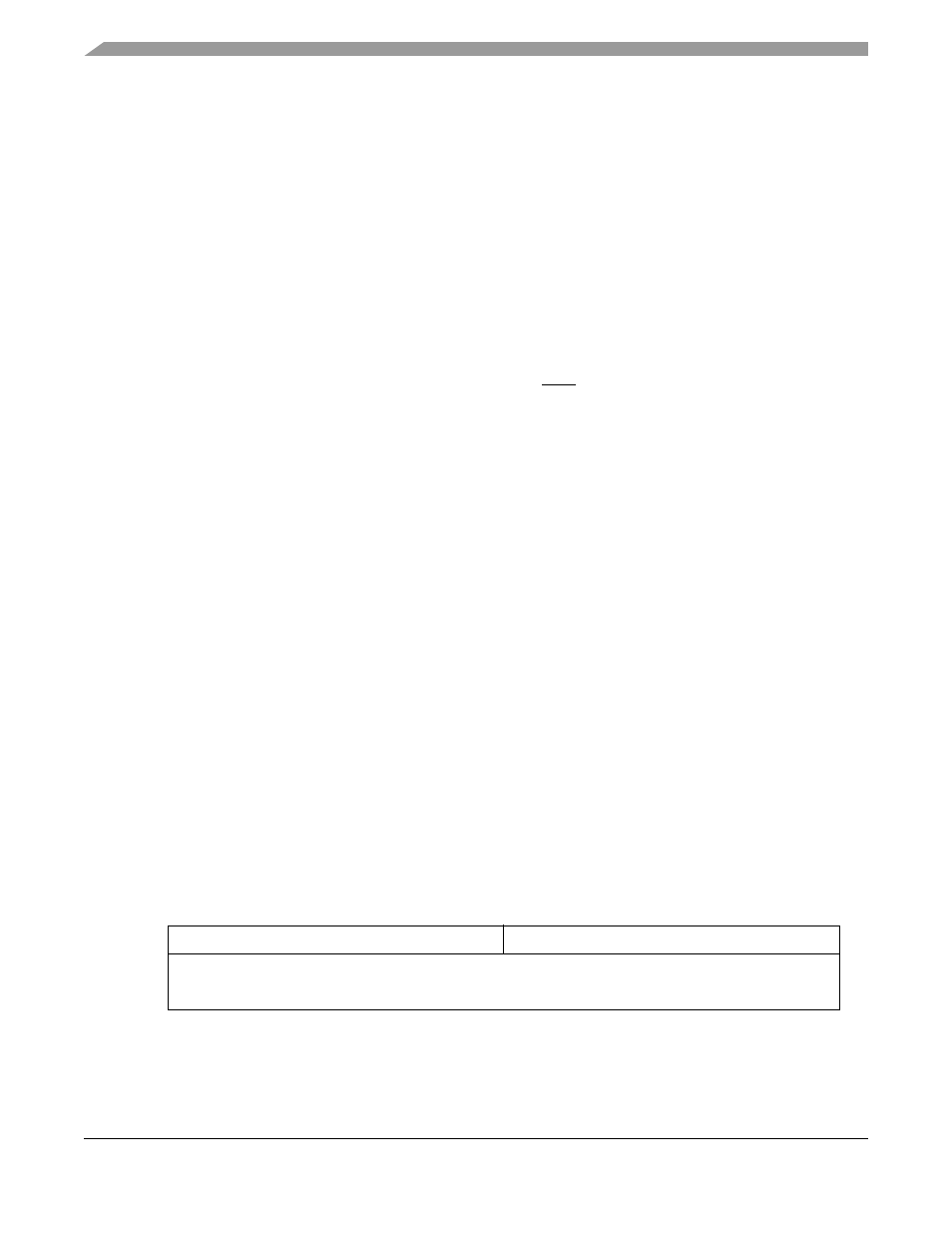

The transparent channel can be programmed to transmit and receive a synchronization pattern if

GFMR[SYNL]

Section 29.2, “General FCC Mode Registers (GFMRx).”

The pattern is defined in

Section 29.4, “FCC Data Synchronization Registers (FDSRx).”

GFMR[SYNL] defines the

SYNC pattern length. The synchronization pattern is shown in

.

The receiver synchronizes on the synchronization pattern located in the FDSR. For instance, if an 8-bit

SYNC is selected, reception begins as soon as these eight bits are received, beginning with the first bit

0

7

8

15

Field

8-Bit Sync Pattern

—

Field

16-Bit Sync Pattern

(Second Byte)

(First Byte)

Figure 37-1. In-Line Synchronization Pattern