2 bus configurations, 1 basic system, Bus configurations -19 – Freescale Semiconductor MPC8260 User Manual

Page 113: Basic system -19, Sonet transmission controller configuration -19, Figure 1-8

Overview

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

1-19

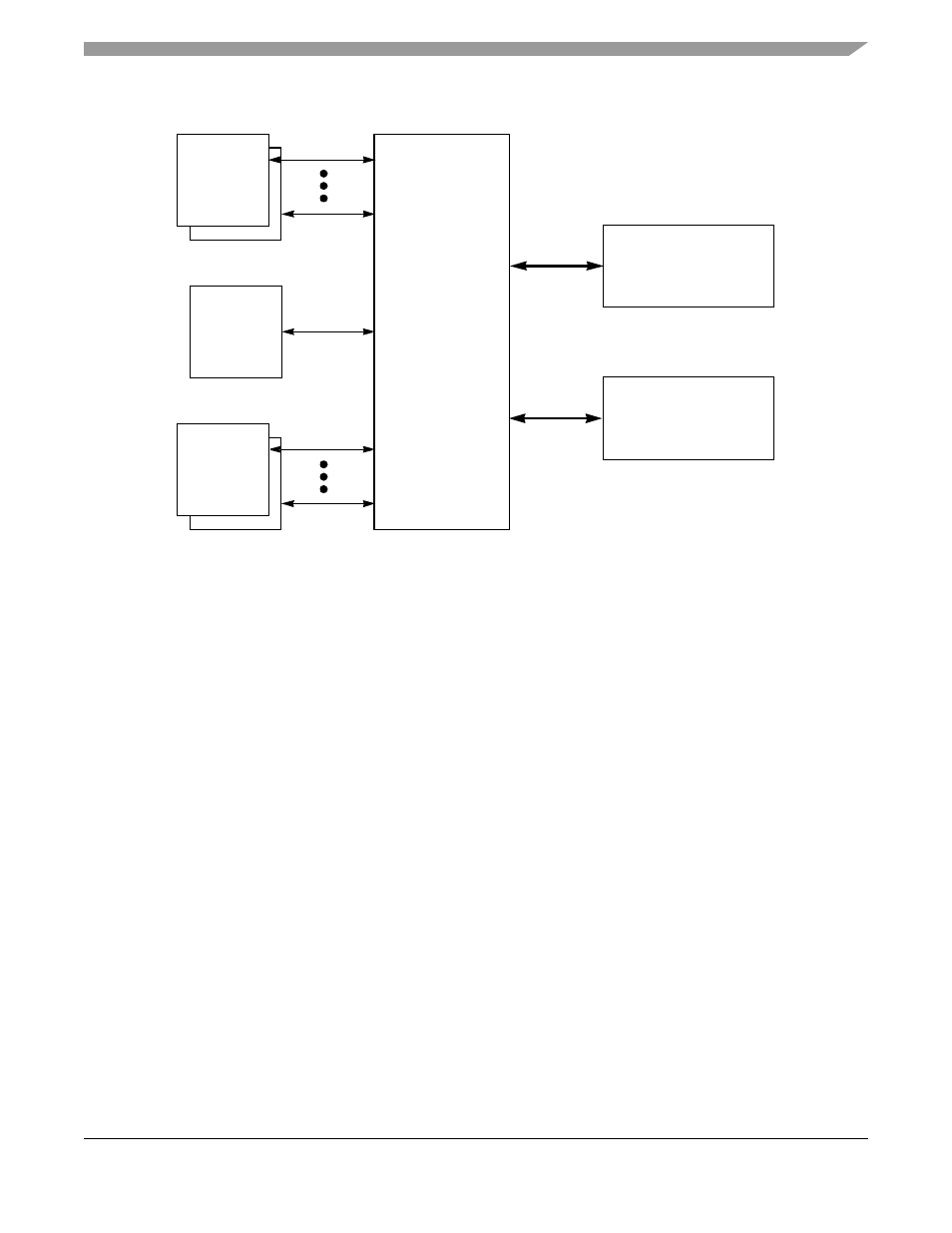

Figure 1-8. SONET Transmission Controller Configuration

In this application, the PowerQUICC II implements super channeling with the MCC. Nine 64-Kbps

channels are combined to form a 576-Kbps channel. The PowerQUICC II at 133 MHz can support up to

sixteen 576-Kbps superchannels. The PowerQUICC II also supports subchanneling (under 64 Kbps) with

its MCC.

1.7.2

Bus Configurations

The following sections describe the following possible bus configurations:

•

Section 1.7.2.1, “Basic System”

•

Section 1.7.2.2, “High-Performance Communication”

•

Section 1.7.2.3, “High-Performance System Microprocessor”

•

(MPC8250, MPC8265, and MPC8266 only)

•

Section 1.7.2.5, “PCI with 155-Mbps ATM”

(MPC8265 and MPC8266 only)

•

Section 1.7.2.6, “PowerQUICC II as PCI Agent”

(MPC8250, MPC8265, and MPC8266 only)

Refer to note at the beginning of

Section 1.7, “Application Examples.”

1.7.2.1

Basic System

In the basic system configuration, shown in

, the PowerQUICC II core is enabled and uses the

64-bit 60x data bus. The 32-bit local bus data is needed to store connection tables for many active ATM

connections. The local bus may also be used to store data that does not need to be heavily processed by the

PowerQUICC II

10/100BaseT

60x Bus

SDRAM/DRAM/SRAM

Channelized Data

Local Bus

SDRAM/DRAM/SRAM

ATM

Connection

Tables

SMC/I2C/SPI/SCC

(10BaseT)

(up to 16 channels)

TDM0

TDM3

MII

Transceiver

576 Kbps

SONET

Transceivers

Slow

Comm

PHY