6 siu interrupt vector register (sivec), Figure 4-18. siu interrupt vector register (sivec), Siu interrupt vector register (sivec) -24 – Freescale Semiconductor MPC8260 User Manual

Page 196

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-24

Freescale Semiconductor

4.3.1.6

SIU Interrupt Vector Register (SIVEC)

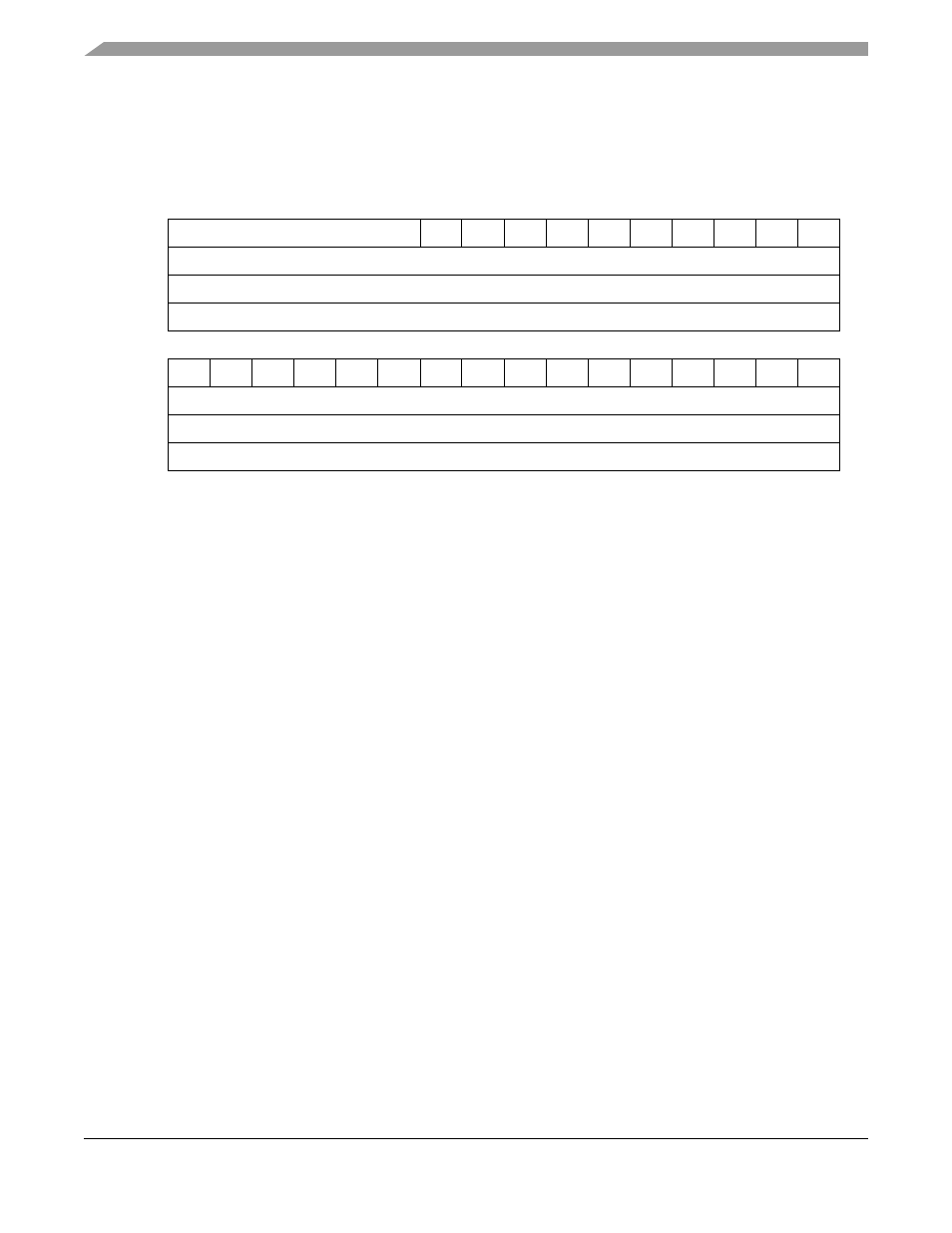

The SIU interrupt vector register (SIVEC), shown in

, contains an 8-bit code representing the

unmasked interrupt source of the highest priority level.

The SIVEC can be read as either a byte, half word, or a word. When read as a byte, a branch table can be

used in which each entry contains one instruction (branch). When read as a half word, each entry can

contain a full routine of up to 256 instructions. The interrupt code is defined such that its two lsbs are

zeroes, allowing indexing into the table, as shown in

.

0

5

6

7

8

9

10

11

12

13

14

15

Field

Interrupt Code

0

0

0

0

0

0

0

0

0

0

Reset

0000_0000_0000_0000

R/W

R

Addr

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Reset

0000_0000_0000_0000

R/W

R

Addr

0x10C06

Figure 4-18. SIU Interrupt Vector Register (SIVEC)