Freescale Semiconductor MPC8260 User Manual

Page 149

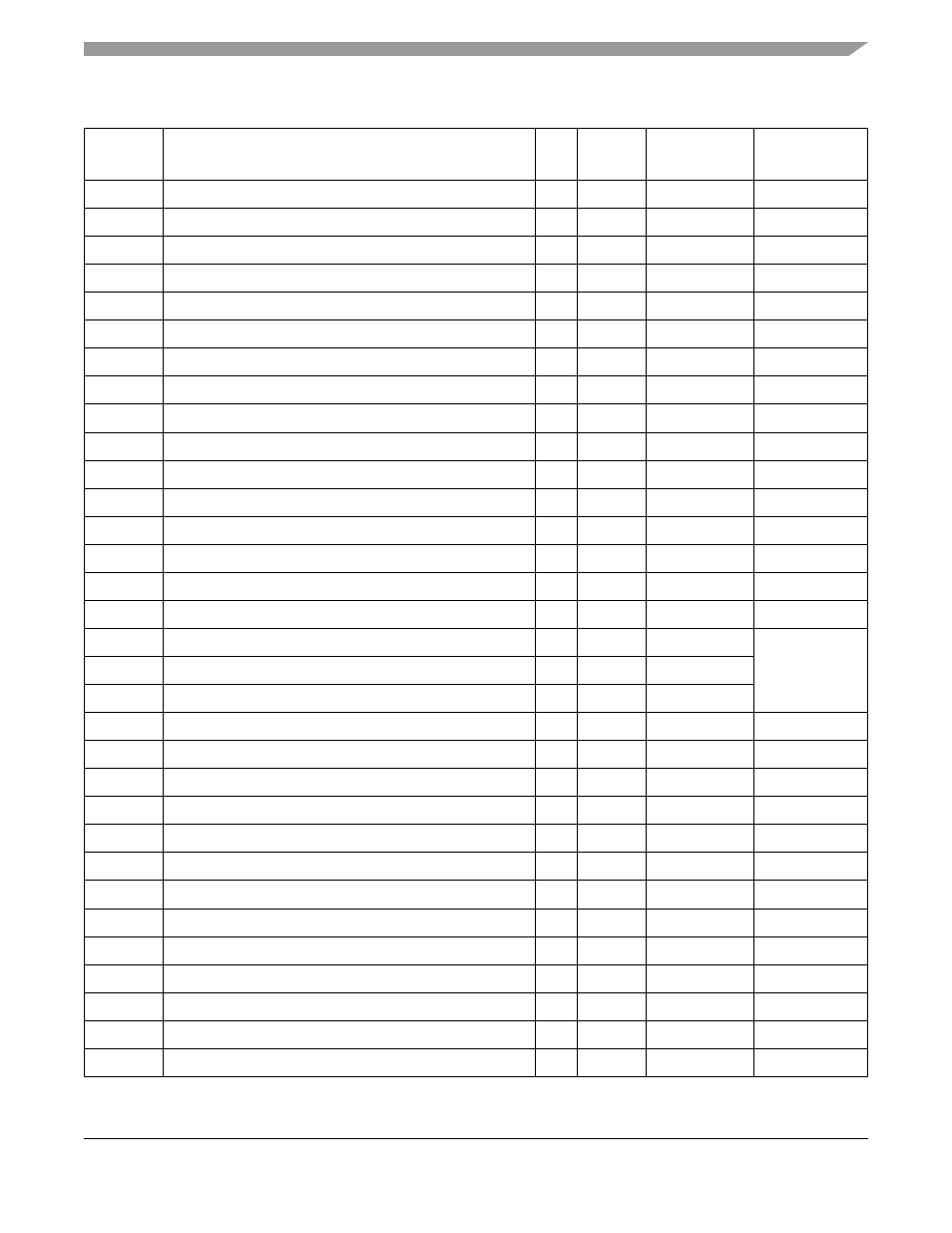

Memory Map

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

3-3

0x1012C

Option register bank 5 (OR5)

R/W

32 bits

undefined

0x10130

Base register bank 6 (BR6)

R/W

32 bits

0x0000_0000

0x10134

Option register bank 6 (OR6)

R/W

32 bits

undefined

0x10138

Base register bank 7 (BR7)

R/W

32 bits

0x0000_0000

0x1013C

Option register bank 7 (OR7)

R/W

32 bits

undefined

0x10140

Base register bank 8 (BR8)

R/W

32 bits

0x0000_0000

0x10144

Option register bank 8 (OR8)

R/W

32 bits

undefined

0x10148

Base register bank 9 (BR9)

R/W

32 bits

0x0000_0000

0x1014C

Option register bank 9 (OR9)

R/W

32 bits

undefined

0x10150

Base register bank 10 (BR10)

R/W

32 bits

0x0000_0000

0x10154

Option register bank 10 (OR10)

R/W

32 bits

undefined

0x10158

Base register bank 11 (BR11)

R/W

32 bits

0x0000_0000

0x1015C

Option register bank 11 (OR11)

R/W

32 bits

undefined

0x10160 Reserved

—

8

bytes

—

—

0x10168

Memory address register (MAR)

R/W

32 bits

undefined

0x1016C

Reserved

—

32 bits

—

—

0x10170

Machine A mode register (MAMR)

R/W

32 bits

0x0004_0000

0x10174

Machine B mode register (MBMR)

R/W

32 bits

0x0004_0000

0x10178

Machine C mode register (MCMR)

R/W

32 bits

0x0004_0000

0x1017C

Reserved

—

48 bits

—

—

0x10184

Memory periodic timer prescaler (MPTPR)

R/W

16 bits

undefined

0x10188

Memory data register (MDR)

R/W

32 bits

undefined

0x1018C

Reserved

—

32 bits

—

—

0x10190

60x bus SDRAM mode register (PSDMR)

R/W

32 bits

0x0000_0000

0x10194

Local bus SDRAM mode register (LSDMR)

R/W

32 bits

0x0000_0000

0x10198

60x bus-assigned UPM refresh timer (PURT)

R/W

8 bits

0x00

0x10199

Reserved

—

24 bits

—

—

0x1019C

60x bus-assigned SDRAM refresh timer (PSRT)

R/W

8 bits

0x00

0x1019D

Reserved

—

24 bits

—

—

0x101A0

Local bus-assigned UPM refresh timer (LURT)

R/W

8 bits

0x00

0x101A1

Reserved

—

24 bits

—

—

0x101A4

Local bus-assigned SDRAM refresh timer (LSRT)

R/W

8 bits

0x00

Table 3-1. Internal Memory Map (continued)

Address

(offset)

Register

R/W

Size

Reset

Section/Page