Table 14-1. possible powerquicc ii applications, 3 communications processor (cp), 1 cpm performance evaluation – Freescale Semiconductor MPC8260 User Manual

Page 552: 2 features, Communications processor (cp) -4, Cpm performance evaluation -4, Features -4, Possible powerquicc ii applications -4

Communications Processor Module Overview

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

14-4

Freescale Semiconductor

14.3

Communications Processor (CP)

The communications processor (CP), also called the RISC microcontroller, is a 32-bit controller for the

CPM that resides on a separate bus from the core and, therefore, can perform tasks independent of the G2

core. The CP handles lower-layer communications tasks and DMA control, freeing the core to handle

higher-layer activities. The CP works with the peripheral controllers and parallel port to implement

user-programmable protocols and manage the serial DMA (SDMA) channels that transfer data between

the I/O channels and memory. It also manages the IDMA (independent DMA) channels and contains an

internal timer used to implement up to 16 additional software timers.

The CP’s architecture and instruction set are optimized for data communications and data processing

required by many wire-line and wireless communications standards.

14.3.1

CPM Performance Evaluation

Because the CP is a single shared resource used by all of the CPM’s communications peripherals, the

combined service requests from all of the communications peripherals must not exceed the CP’s capacity.

The amount of processing required by a particular communications peripheral depends on the mode in

which the peripheral is configured and the maximum rate at which the channel requests service. To

determine if CPM performance and bus bandwidth consumption of a given configuration is valid, users

should consult the “MPC8260 CPM Performance Evaluator,” which is located under “Application

Software” on a device’s product page at www.freescale.com.

14.3.2

Features

The following is a list of the CP’s important features.

•

One system clock cycle per instruction

•

32-bit instruction object code

•

Executes code from internal ROM or RAM

•

32-bit ALU data path

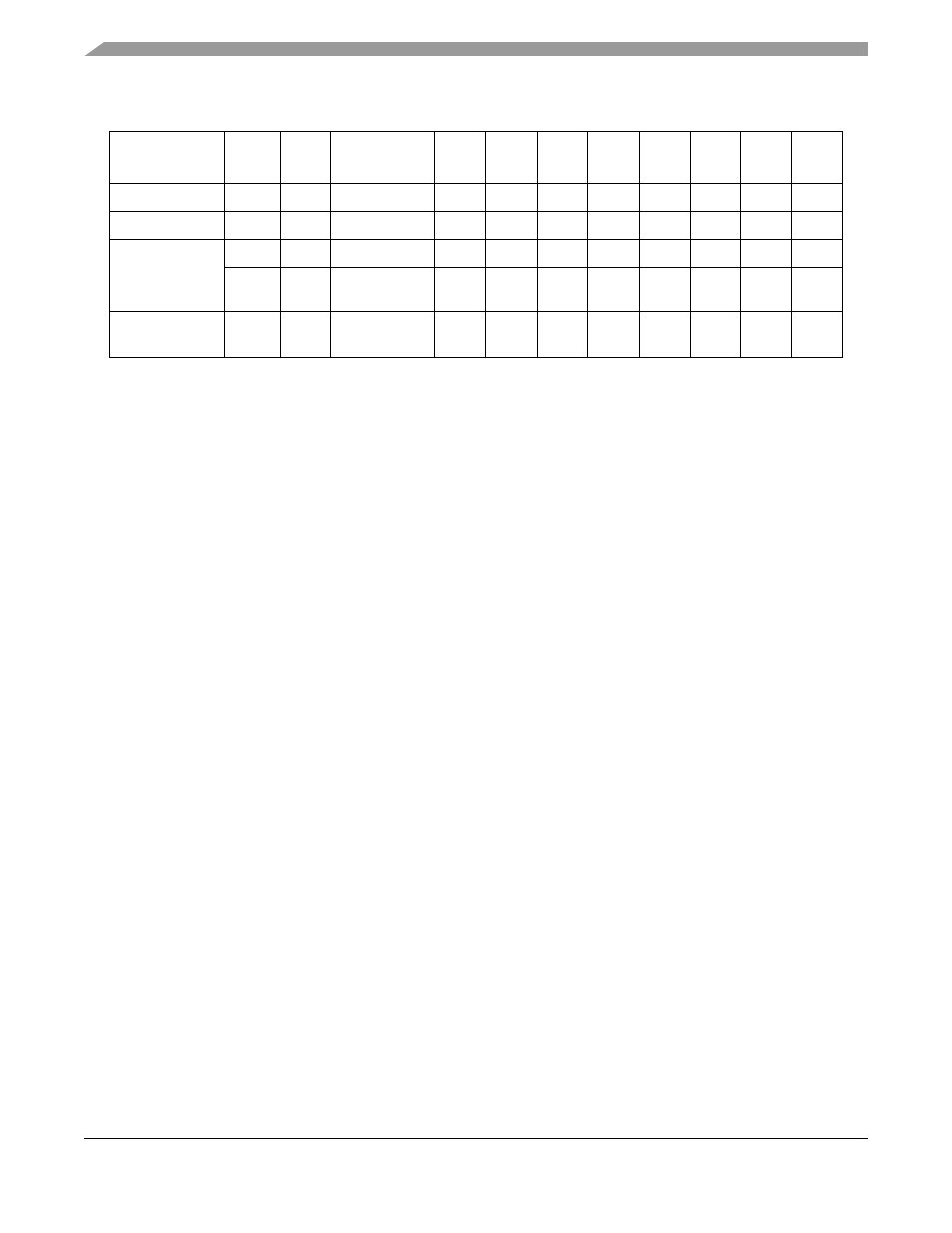

Table 14-1. Possible PowerQUICC II Applications

Application

MCC1

1

1

Not on the MPC8250 and the MPC8255.

MCC2

FCC1

FCC2

FCC3

2

2

Not on the MPC8255.

SCC1

SCC2

SCC3

SCC4

SMC1 SMC2

ISDN router

4 E1

4 E1

FEnet or ATM

FEnet

UART

UART

UART

UART

ATM switch

ATM

FEnet

UART

ATM access

ATM

FEnet

FEnet

E3 or

E1’s

E3 or

E1’s

ATM

UART

GSM mobile

switching center

E1’s

FEnet or ATM

Backbone

10 M

HDLC

10 M

HDLC