Port b dedicated pin assignment (pparb = 1) -12, Table 40-6 – Freescale Semiconductor MPC8260 User Manual

Page 1290

Parallel I/O Ports

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

40-12

Freescale Semiconductor

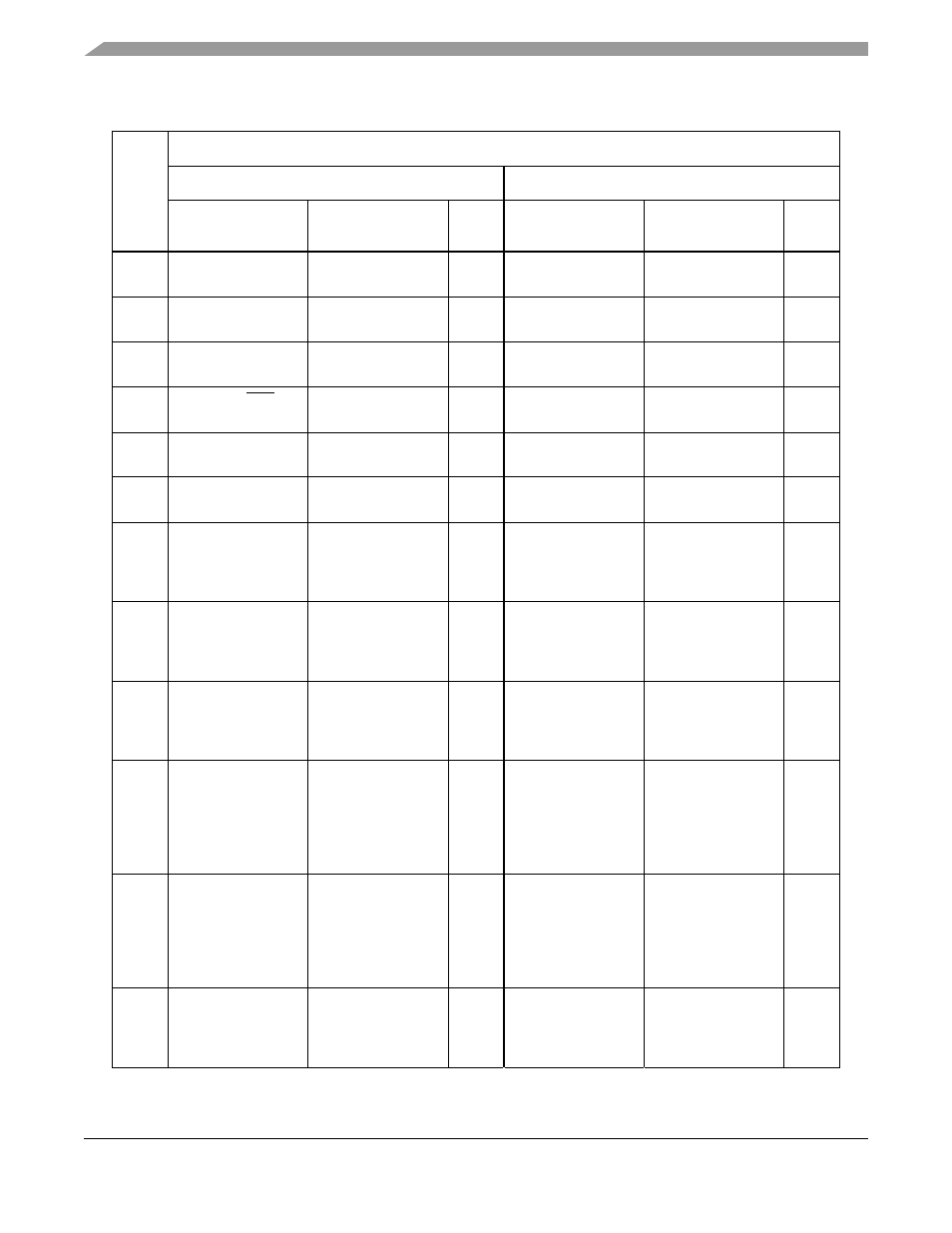

Table 40-6. Port B Dedicated Pin Assignment (PPARB = 1)

Pin

Pin Function

PSORB = 0

PSORB = 1

PDIRB = 1 (Output)

PDIRB = 0 (Input)

Defaul

t Input

PDIRB = 1 (Output)

PDIRB = 0 (Input or

Inout if Specified)

Defaul

t Input

PB31

FCC2: TX_ER

MII

FCC2: RxSOC

1

UTOPIA

GND

TDM_B2: L1TXD

Inout

GND

PB30

FCC2: TxSOC

1

UTOPIA

FCC2: RX_DV

MII

GND

TDM_B2: L1RXD

Inout

GND

PB29

FCC2: RxClav

1

UTOPIA slave

FCC2: RxClav

1

UTOPIA master

GND

FCC2: TX_EN

MII

TDM_B2: L1RSYNC

GND

PB28

FCC2: RTS

FCC2: RX_ER

MII

GND

SCC1: TXD

TDM_B2:

L1TSYNC/GRANT

GND

PB27

FCC2: TxD[0]

1

UTOPIA 8

FCC2: COL

MII

GND

TDM_C2: L1TXD

Inout

GND

PB26

FCC2: TxD[1]

1

UTOPIA 8

FCC2: CRS

MII

GND

TDM_C2: L1RXD

Inout

GND

PB25

FCC2: TxD[4]

1

UTOPIA 8

FCC2: TxD[3]

MII/HDLC nibble

TDM_A1: L1TXD[3]

Nibble

TDM_C2:

L1TSYNC/GRANT

GND

PB24

FCC2: TxD[5]

1

UTOPIA 8

FCC2: TxD[2]

MII/HDLC nibble

TDM_A1: L1RXD[3]

Nibble

GND

TDM_C2: L1RSYNC

GND

PB23

FCC2: TxD[6]

1

UTOPIA

FCC2: TxD[1]

MII/HDLC nibble

TDM_A1: L1RXD[2]

Nibble

GND

TDM_D2: L1TXD

Inout

GND

PB22

FCC2: TxD[7]

1

UTOPIA

FCC2: TxD[0]

MII/HDLC nibble

FCC2: TxD

HDLC/transp. serial

TDM_A1: L1RXD[1]

Nibble

GND

TDM_D2: L1RXD

Inout

GND

PB21

FCC2: RxD[7]

UTOPIA 8

FCC2: RxD[0]

MII/HDLC nibble

FCC2: RxD

HDLC/transp. serial

GND

TDM_A1: L1TXD[2]

Nibble

TDM_D2:

L1TSYNC/GRANT

GND

PB20

FCC2: RxD[6]

UTOPIA 8

FCC2: RxD[1]

MII/HDLC nibble

GND

TDM_A1-L1TXD[1]

Nibble

TDM_D2: L1RSYNC

GND