Figure 30-8. vc pointer address compression, 3 misinserted cells, 4 receive raw cell queue – Freescale Semiconductor MPC8260 User Manual

Page 938: Misinserted cells -18, Receive raw cell queue -18, Vc pointer address compression -18, Hown in, Table 30-6

ATM Controller and AAL0, AAL1, and AAL5

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

30-18

Freescale Semiconductor

shows the VC pointer address compression from

.

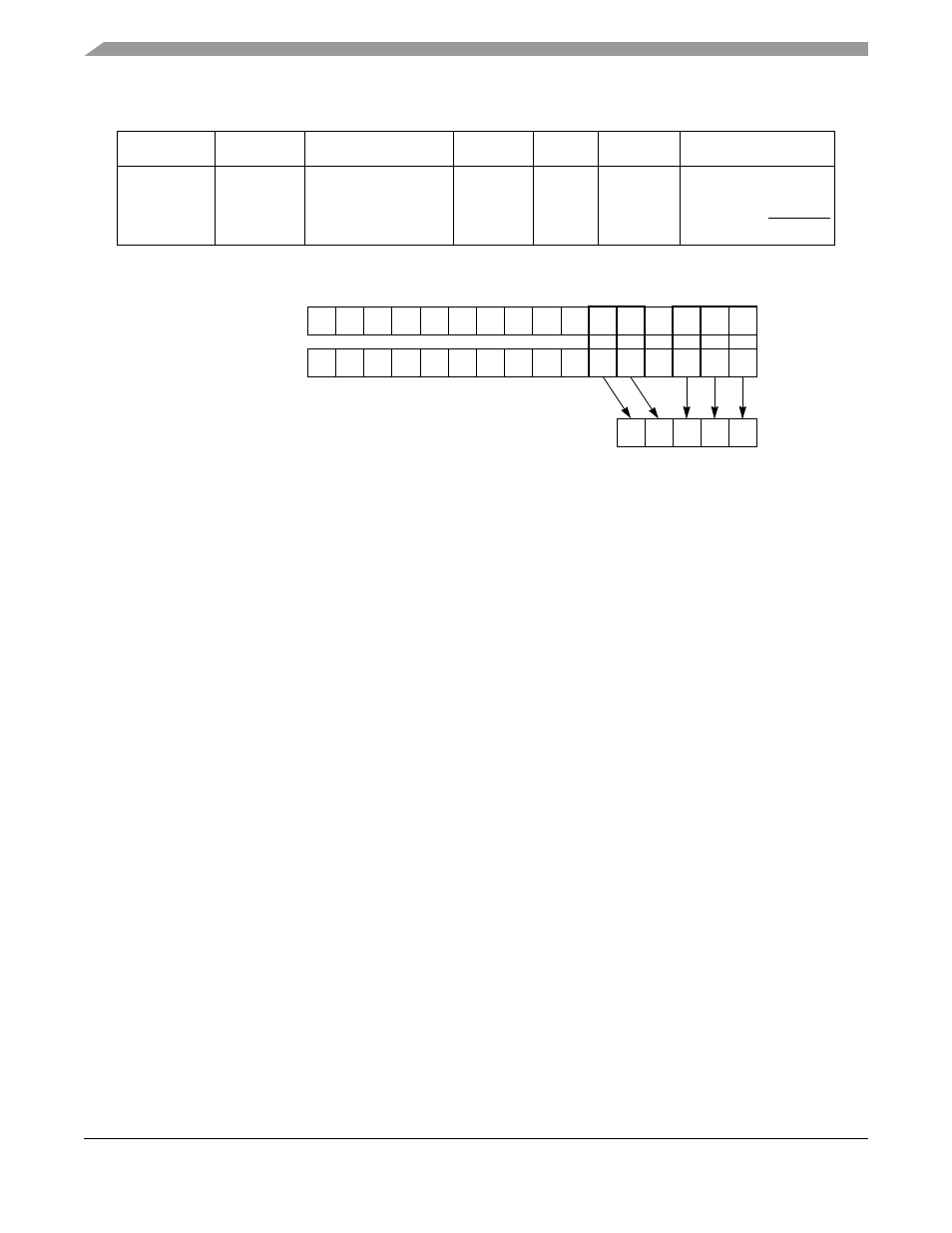

Figure 30-8. VC Pointer Address Compression

30.4.3

Misinserted Cells

If the address lookup mechanism cannot find a match (MS=1), the cell is discarded and ATM layer

statistics are updated, as described in

Section 30.8, “ATM Layer Statistics.”

30.4.4

Receive Raw Cell Queue

Channel one in the RCT is reserved as a raw cell queue. The user should program channel one to operate

in AAL0 protocol. The receive raw cell queue is used for removing management cells from the regular cell

flow to the host. When a management cell is sent to the receive raw cell queue, the CP sets RxBD[OAM].

The ALL0 BD specifies the channel code associated with the current OAM cell.

The following are optionally removed from the regular flow and sent to the raw cell queue:

•

Segment F5 OAM (PTI = 0b100). To enable F5 segment filtering, set RCT[SEGF].

•

End-to-end F5 OAM (PTI = 0b101). To enable F5 end-to-end filtering, set RCT[ENDF].

•

RM cells (PTI = 0b110). When ABR flow is enabled the cells are terminated internally; otherwise,

they are sent to the raw cell queue.

•

Reserved PTI value (PTI = 0b111). Always sent to the raw cell queue.

•

VCI value: 3, 4, 6, 7–15. To enable VCI filtering set the associated bit in the VCIF entry in the

parameter RAM.

shows a flowchart of the ATM cell flow.

Table 30-6. VC-Level Table Entry Address Calculation Example

VCT_BASE

VCOffset

VC-Level Table Size

VC_MASK

VCI

VC Pointer

VC Entry Address

0x0084_0000

0x0100

32 entries

0x0037

0x0031

0x19

VC Base = 0x840000

0x100 x 4 = 0x000400

0x19 x 4 = 0x000064

0x840464

0

0

0

0

0

0

1

1

0

0

0

1

0

0

0

0

0

0

1

1

0

1

1

1

0

0

1

VCI

VC_MASK

VC Pointer

1

1

0

0

0

0

0

0

0

0