Figure 11-54. external termination of gpcm access, 3 boot chip-select operation, Boot chip-select operation -62 – Freescale Semiconductor MPC8260 User Manual

Page 480: External termination of gpcm access -62, Boot bank field values after reset -62

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

11-62

Freescale Semiconductor

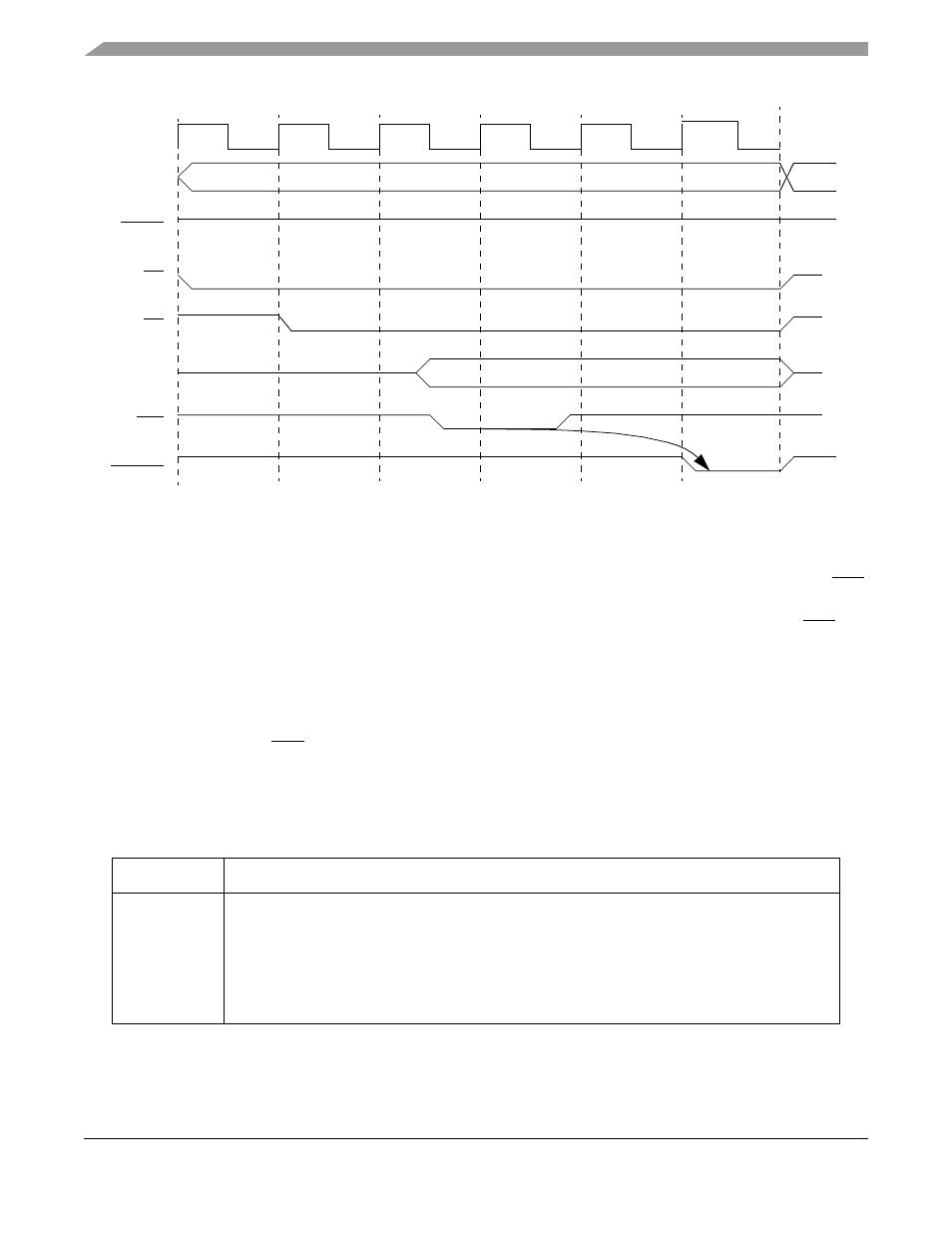

Figure 11-54. External Termination of GPCM Access

11.5.3

Boot Chip-Select Operation

Boot chip-select operation allows address decoding for a boot ROM before system initialization. The CS0

signal is the boot chip-select output; its operation differs from the other external chip-select outputs on

system reset. When the PowerQUICC II internal core begins accessing memory at system reset, CS0 is

asserted for every address in the boot address range, unless an internal register is accessed. The address

range is configured during reset.

The boot chip-select also provides a programmable port size during system reset by using the

configuration mechanism described in

Section 5.4, “Reset Configuration.”

The boot chip-select does not

provide write protection. CS0 operates this way until the first write to OR0 and it can be used as any other

chip-select register once the preferred address range is loaded into BR0. After the first write to OR0, the

boot chip-select can be restarted only on hardware reset.

describes the initial values of the boot

bank in the memory controller.

Table 11-33. . Boot Bank Field Values after Reset

Register

Setting

BR0

BA From hard reset configuration word. See

Section 5.4.1, “Hard Reset Configuration Word

.”

PS From hard reset configuration word. See

Section 5.4.1, “Hard Reset Configuration Word

DECC0

WP0

MS000

EMEMC From hard reset configuration word. See

Section 5.4.1, “Hard Reset Configuration Word

V 1

Clock

Address

BCTL

x

CS

OE

D

GTA

PSDVAL