12 scc bisync receive bd (rxbd), Figure 23-6. scc bisync rxbd, Scc b – Freescale Semiconductor MPC8260 User Manual

Page 762: Scc bisync rxbd -12, Command is issued. • the

SCC BISYNC Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

23-12

Freescale Semiconductor

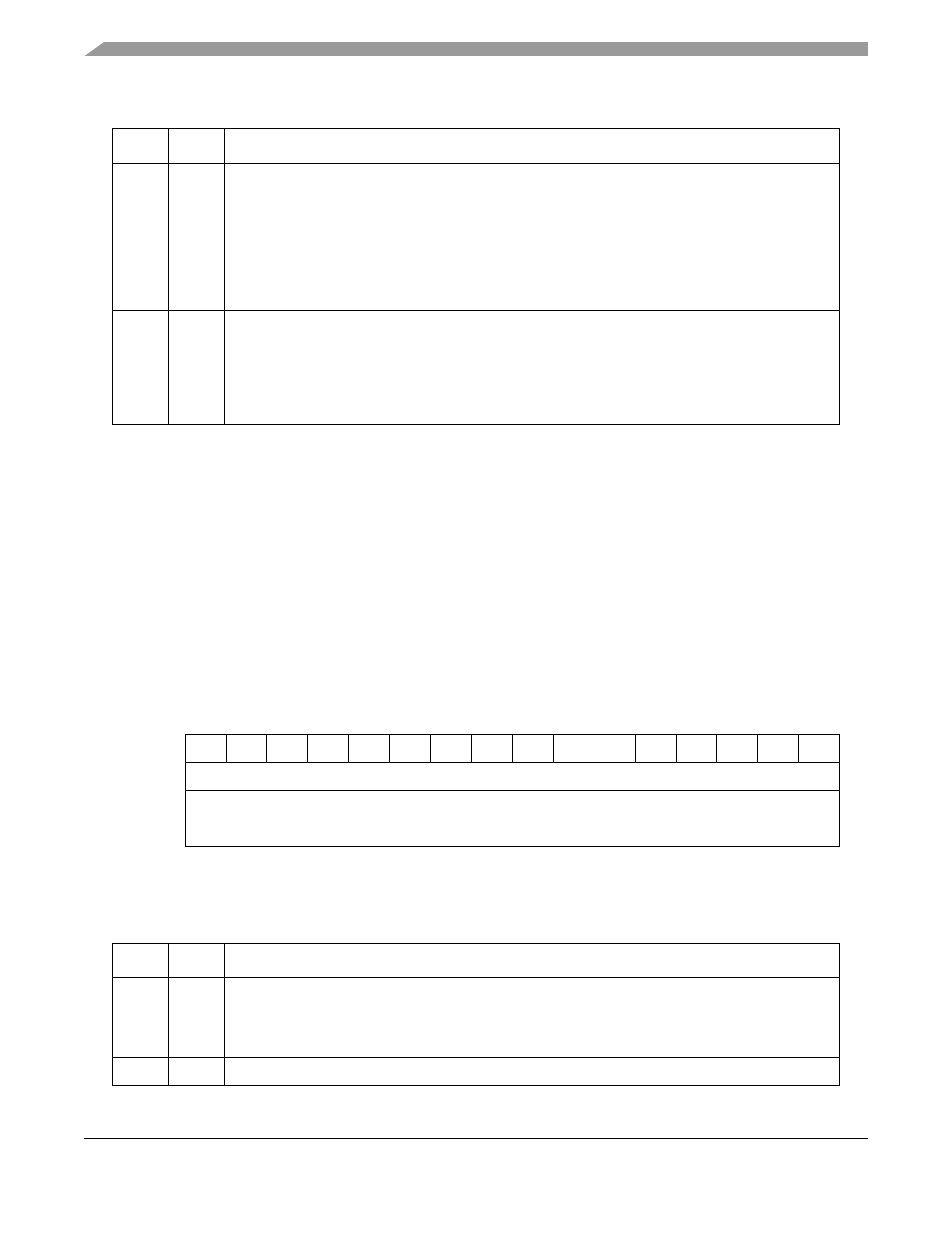

23.12 SCC BISYNC Receive BD (RxBD)

The CP uses BDs to report on each buffer received. It closes the buffer, generates a maskable interrupt,

and starts receiving data into the next buffer after any of the following:

•

A user-defined control character is received.

•

An error is detected.

•

A full receive buffer is detected.

•

The

ENTER

HUNT

MODE

command is issued.

•

The

CLOSE

RX

BD

command is issued.

shows the SCC BISYNC RxBD.

describes SCC BISYNC RxBD status and control fields.

12–13

RPM

Receiver parity mode. Selects the type of parity check that the receiver performs. RPM can be

modified on-the-fly and is ignored unless CRC = 11 (LRC). Receive parity errors cannot be disabled

but can be ignored.

00 Odd parity. The transmitter counts ones in the data word. If the sum is not odd, the parity bit is

set to ensure an odd number. An even sum indicates a transmission error.

01 Low parity. If the parity bit is not low, a parity error is reported.

10 Even parity. An even number must result from the calculation performed at both ends of the line.

11 High parity. If the parity bit is not high, a parity error is reported.

14–15

TPM

Transmitter parity mode. Selects the type of parity the transmitter performs and can be modified

on-the-fly. TPM is ignored unless CRC = 11 (LRC).

00 Odd parity.

01 Force low parity (always send a zero in the parity bit position).

10 Even parity.

11 Force high parity (always send a one in the parity bit position).

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Offset + 0

E

—

W

I

C

B

CM

—

DE

—

DL

PR

CR

OV

CD

Offset + 2

Data Length

Offset + 4

Rx Data Buffer Pointer

Offset + 6

Figure 23-6. SCC BISYNC RxBD

Table 23-11. SCC BISYNC RxBD Status and Control Field Descriptions

Bits

Name

Description

0

E

Empty.

0 The buffer is full or stopped receiving because of an error. The core can read or write any fields

of this RxBD. The CP does not use this BD as long as the E bit is zero.

1 The buffer is not full. The CP controls this BD and buffer. The core should not update this BD.

1

—

Reserved, should be cleared.

Table 23-10. PSMR Field Descriptions (continued)

Bits

Name

Description