Freescale Semiconductor MPC8260 User Manual

Page 1310

Reference Manual (Rev 1) Errata

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

B-8

Freescale Semiconductor

occurs every 256 serial transmit clocks. The polling algorithm depends on the

FCC configuration, as shown in the following equations:

The user, however, can request that the CP begin processing the new frame/buffer

without waiting the normal polling time. For immediate processing, after setting

TxBD[R], set the transmit-on-demand (TOD) bit in the transmit-on-demand

register (FTODR) twice to activate. If TOD is set only once, the new

frame/buffer will not be transmitted until the next periodic polling request.

29.10.1.1, 29-16

In step 3 of the re-initialization procedure, the command issued from CPCR must

be a RESTART_TX, not INIT_TX_PARAMS.

30.2.2, 30-7

In the second paragraph, replace the sentence that begins, “The cell includes...,”

with the following (changes appear in boldface):

The cell includes: 4 bytes ATM cell header, 1 byte HEC, which can be checked

by setting FPSMR[HECC] (refer to Table 30-47), and 48 bytes payload.

[Note that the description of HECC referred to above is also contained in this

document as an errata for Section 30.13.2. The description is not shown in the

manual]

30.10.1.3, 30-43

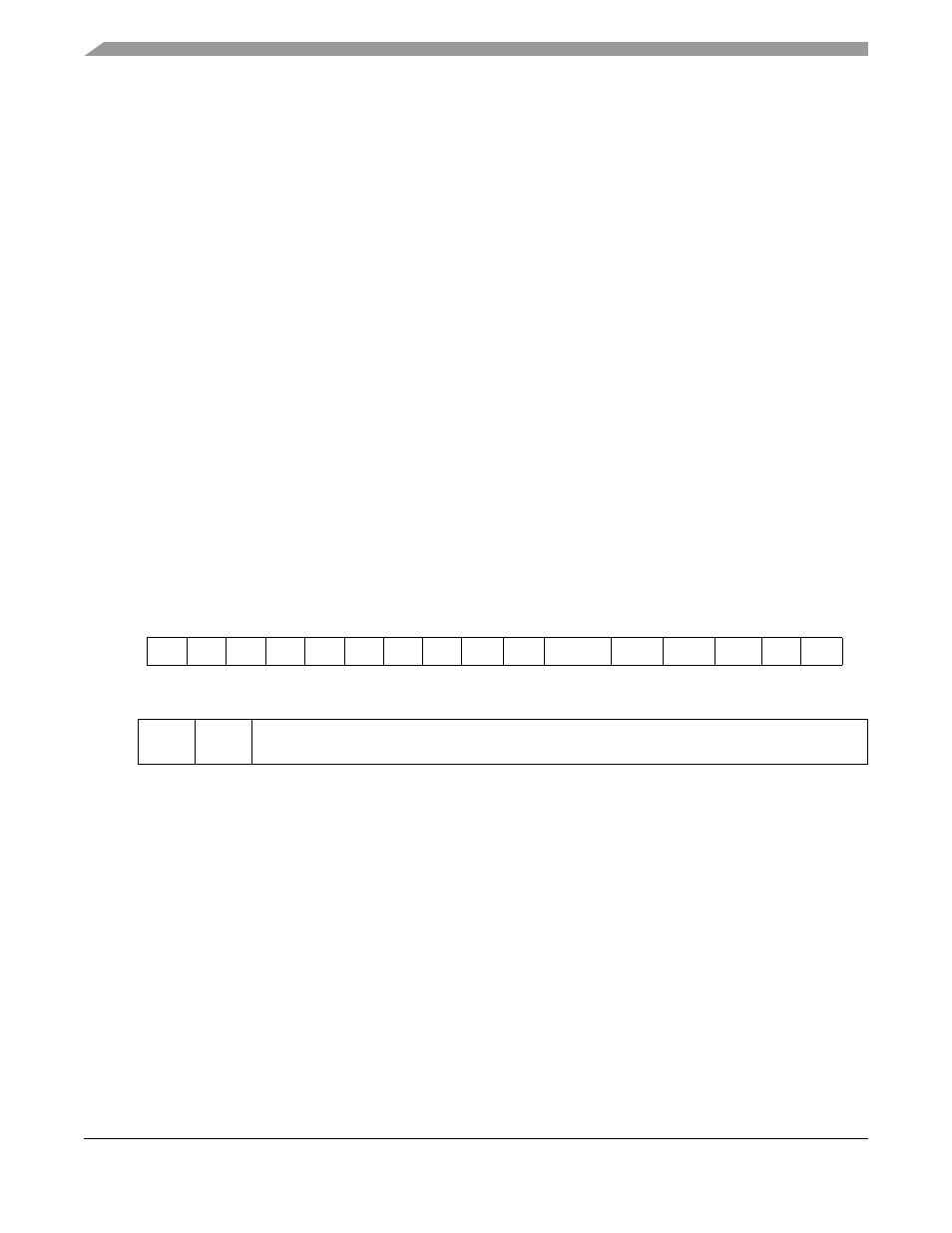

Add GBL at bit 2 in Figure 30-23 and Table 30-14 as shown in the following:

30.10.5.3, 30-74

In Table 30-34, the alignment column for AAL1 and ALL5 receive buffers should

state “Burst-aligned (recommended).”

30.10.5.4, 30-76

In Table 30-35, the description for RXDBPTR at offset 0x04 should state the

following (change appears in boldface):

Rx data buffer pointer. Points to the first location of the associated buffer; may

reside in internal or external memory. It is recommended that the pointer be

burst-aligned.

30.10.5.5, 30-77

In Table 30-35, the description for RXDBPTR at offset 0x04 should state the

following (change appears in boldface):

Rx data buffer pointer. Points to the first location of the associated buffer; may

reside in internal or external memory. It is recommended that the pointer be

burst-aligned.

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

0

0

GBL

0

0

0

ALB CTB REM

0

IMA_EN

1

1

MPC8264 and MPC8266 only.

UEAD

CUAB EVPT

0

ALM

2

GBL

Global. Asserting GBL enables snooping of connection tables. GBL should not be asserted if any of

the related DMAs will access the local bus.

Fast Ethernet:

256 clocks / 25 MHz = 10

µs

10BaseT:

256 clocks / 2.5 MHz = 100

µs