1 interrupt configuration, Figure 4-8. powerquicc ii interrupt structure, Interrupt configuration -8 – Freescale Semiconductor MPC8260 User Manual

Page 180: Powerquicc ii interrupt structure -8

System Interface Unit (SIU)

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

4-8

Freescale Semiconductor

4.2.1

Interrupt Configuration

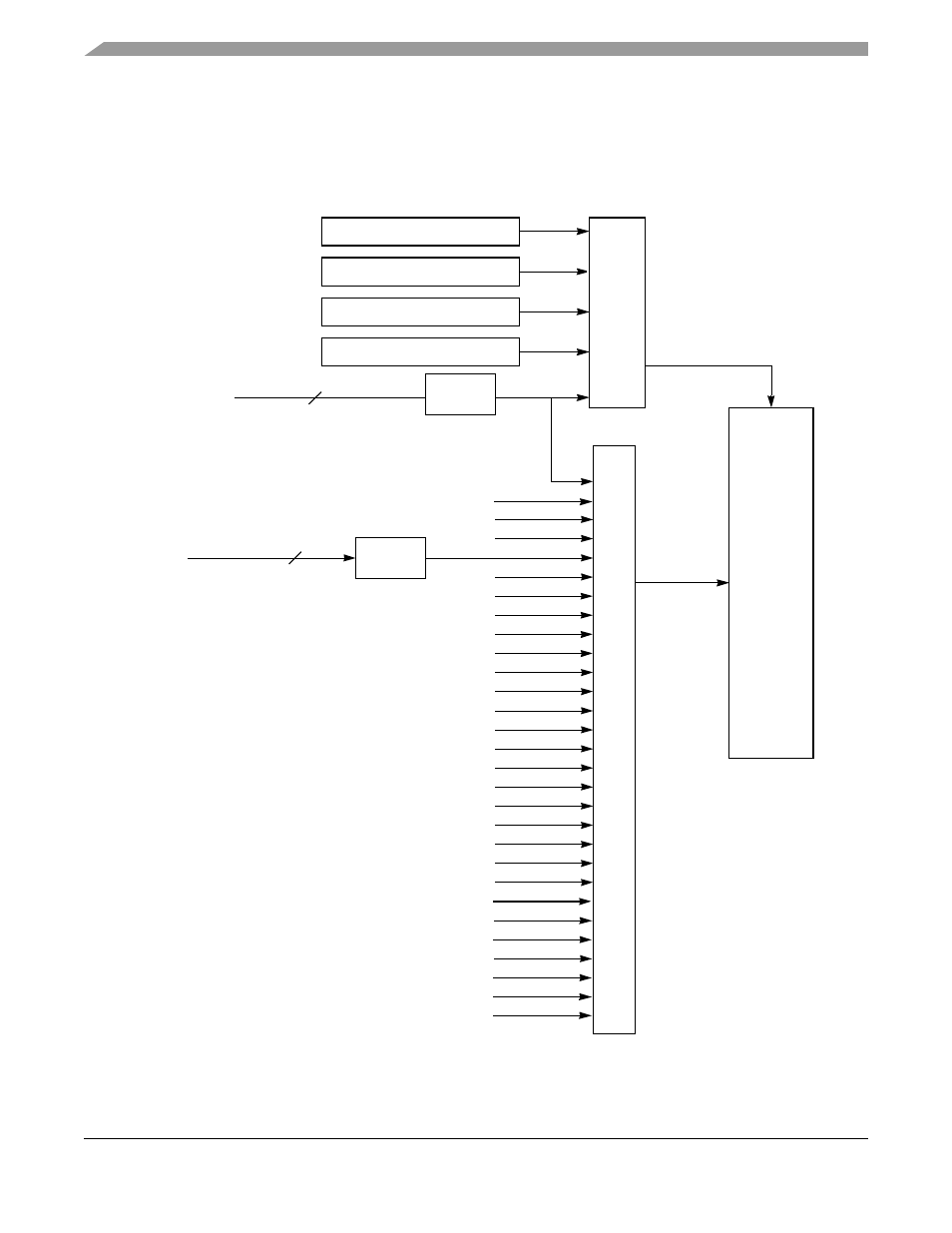

shows the PowerQUICC II interrupt structure. The interrupt controller receives interrupts from

internal sources, such as the PIT or TMCNT, from the CPM, the PCI bridge (with its own interrupt

controller), and from external pins (port C parallel I/O pins).

Figure 4-8. PowerQUICC II Interrupt Structure

MCP

IRQ[0–7]

INT

OR

G2

Core

Port C[0–15]

Timer1

Timer2

Timer3

Timer4

SCC3

SCC4

SMC1

SPI

I2C

SMC2

Software watchdog timer

IRQ0

In

te

rr

u

p

t Cont

ro

ller

IDMA1

IDMA2

RISC Timers

Fall/

Level

SCC2

SCC1

MCC1

2

FCC3

FCC2

FCC1

PIT

TMCNT

Edge/

Fall

IDMA3

IDMA4

SDMA

MCC2

16

8

TC layers

3

Memory controller data errors

PCI

1

Bus monitor address only

IRQ[1–7]

Notes

1

MPC8250, MPC8265, and MPC8266 only

2

Not on MPC8250 and MPC8255

3

MPC8264 and MPC8266 only

PCI

1