Figure 9-89. dma chain of segment descriptors, 1 descriptor in big endian mode, Descriptor in big endian mode -96 – Freescale Semiconductor MPC8260 User Manual

Page 402: Dma chain of segment descriptors -96

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-96

Freescale Semiconductor

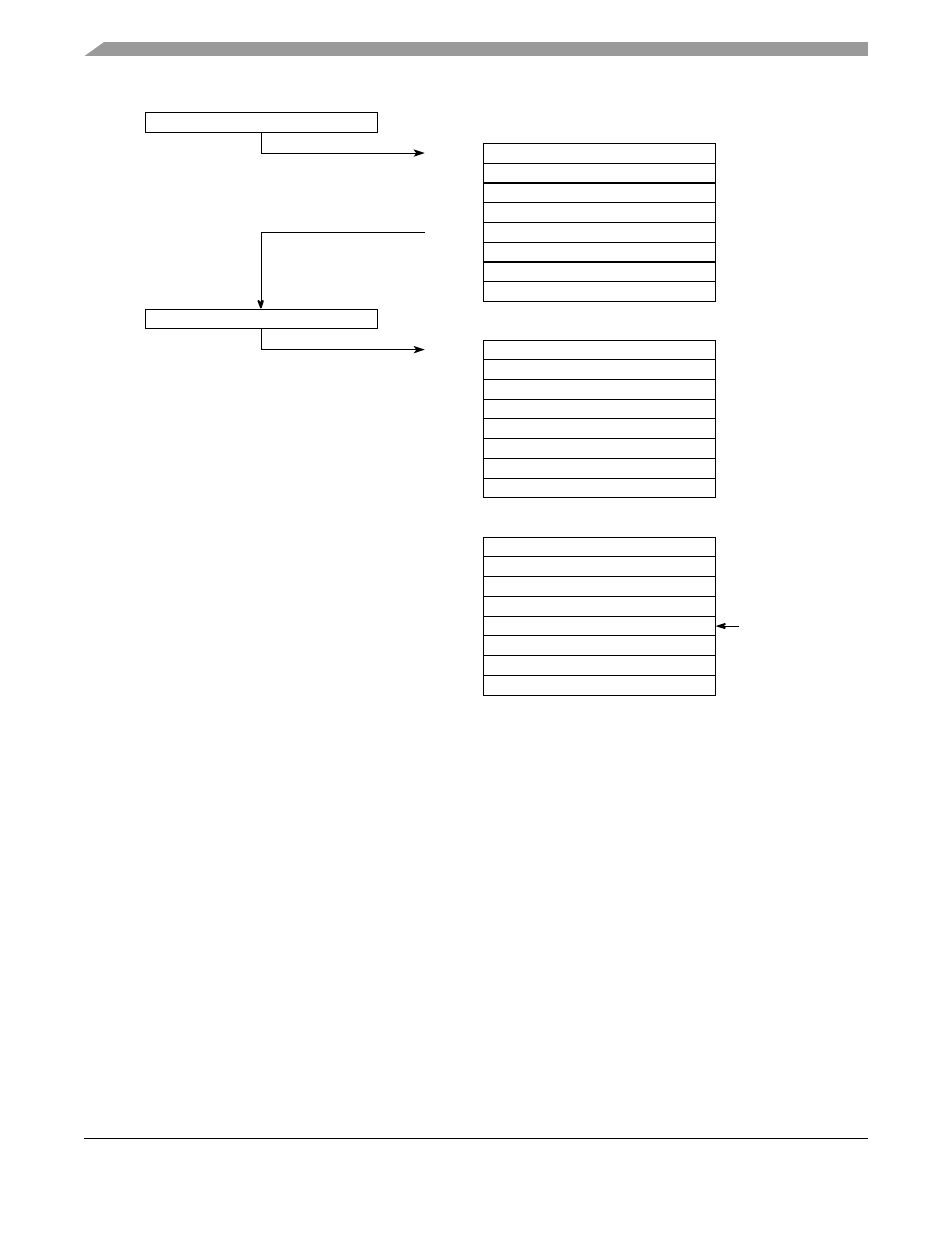

Figure 9-89. DMA Chain of Segment Descriptors

9.13.2.1

Descriptor in Big Endian Mode

In big endian mode, the descriptor in 60x memory should be programmed such that data appears in

ascending significant-byte order. If segment descriptors are written to memory located in the 60x bus, they

should be treated like they are translated from big endian to little endian mode.

Example: Big Endian mode descriptor’s data structure. Note that the descriptor structure must be aligned

on an 8-word boundary.

struct {

double a;

/* 0x1122334455667788 double word

*/

double b;

/* 0x55667788aabbccdd double word

*/

double c;

/* 0x8765432101234567 double word */

double d;

/* 0x0123456789abcdef double word */

} Descriptor;

Results: Source Address = 0x44332211

Destination Address = 0x88776655

Next Descriptor Address = 0x21436587

Source address

Local memory or PCI memory

Reserved

Destination address

Reserved

Next descriptor

Reserved

Byte count

Reserved

0x00

0x04

0x08

0x0C

0x10

0x14

0x18

0x1C

Offset

0

31

Source address

Reserved

Destination address

Reserved

Next descriptor

Reserved

Byte count

Reserved

0x00

0x04

0x08

0x0C

0x10

0x14

0x18

0x1C

Offset

0

31

Source address

Reserved

Destination address

Reserved

Next descriptor

Reserved

Byte count

Reserved

0x00

0x04

0x08

0x0C

0x10

0x14

0x18

0x1C

Offset

0

31

Descriptor 0

Descriptor 1

Descriptor N

(last)

EOTD=1

Current descriptor address register

0

31

Next descriptor address register

0

31