Table 25-5. reception errors, 17 ethernet mode register (psmr), Figure 25-5. ethernet mode register (psmr) – Freescale Semiconductor MPC8260 User Manual

Page 798: Ethernet mode register (psmr) -14, Reception errors -14, Table 25-5 describes reception errors

SCC Ethernet Mode

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

25-14

Freescale Semiconductor

describes reception errors.

25.17 Ethernet Mode Register (PSMR)

In Ethernet mode, the protocol-specific mode register (PSMR), shown in

, is used as the

Ethernet mode register.

describes PSMR fields.

Late collision

When this error occurs, the channel stops sending the buffer, closes it, sets SCCE[TXE] and

the LC bit in the TxBD. The channel resumes transmission after it receives the

RESTART

TRANSMIT

command. This error is discussed further in the definition of PSMR[LCW].

Heartbeat

Some transceivers have a heartbeat (signal-quality error) self-test. To signify a good self-test,

the transceiver indicates a collision to the

PowerQUICC II within 20 clocks after the Ethernet

controller sends a frame. This heartbeat condition does not imply a collision error, but that the

transceiver seems to be functioning properly. If SCCE[HBC] = 1 and the

PowerQUICC II does not

detect a heartbeat condition after sending a frame, a heartbeat error occurs; the channel

closes the buffer, sets the HB bit in the TxBD, and generates the TXE interrupt if it is enabled.

Table 25-5. Reception Errors

Error

Description

Overrun

The Ethernet controller maintains an internal FIFO for receiving data. When it overruns, the channel

writes the received byte over the previously received byte. The previous byte and frame status are lost.

The channel closes the buffer, sets RxBD[OV] and SCCE[RXF], and increments the discarded frame

counter (DISFC). The receiver then enters hunt mode.

Busy

A frame was received and discarded because of a lack of buffers. The channel sets SCCE[BSY] and

increments DISFC. The receiver then enters hunt mode.

Non-Octet

Error

(Dribbling

Bits)

The Ethernet controller handles up to seven dribbling bits when the receive frame terminates nonoctet

aligned. It checks the CRC of the frame on the last octet boundary. If there is a CRC error, a frame

nonoctet aligned error is reported, SCCE[RXF] is set, and the alignment error counter is incremented. If

there is no CRC error, no error is reported. The receiver then enters hunt mode.

CRC

When a CRC error occurs, the channel closes the buffer, sets SCCE[RXF] and CR in the RxBD, and

increments the CRC error counter (CRCEC). After receiving a frame with a CRC error, the receiver

enters hunt mode. CRC checking cannot be disabled, but CRC errors can be ignored if checking is not

required.

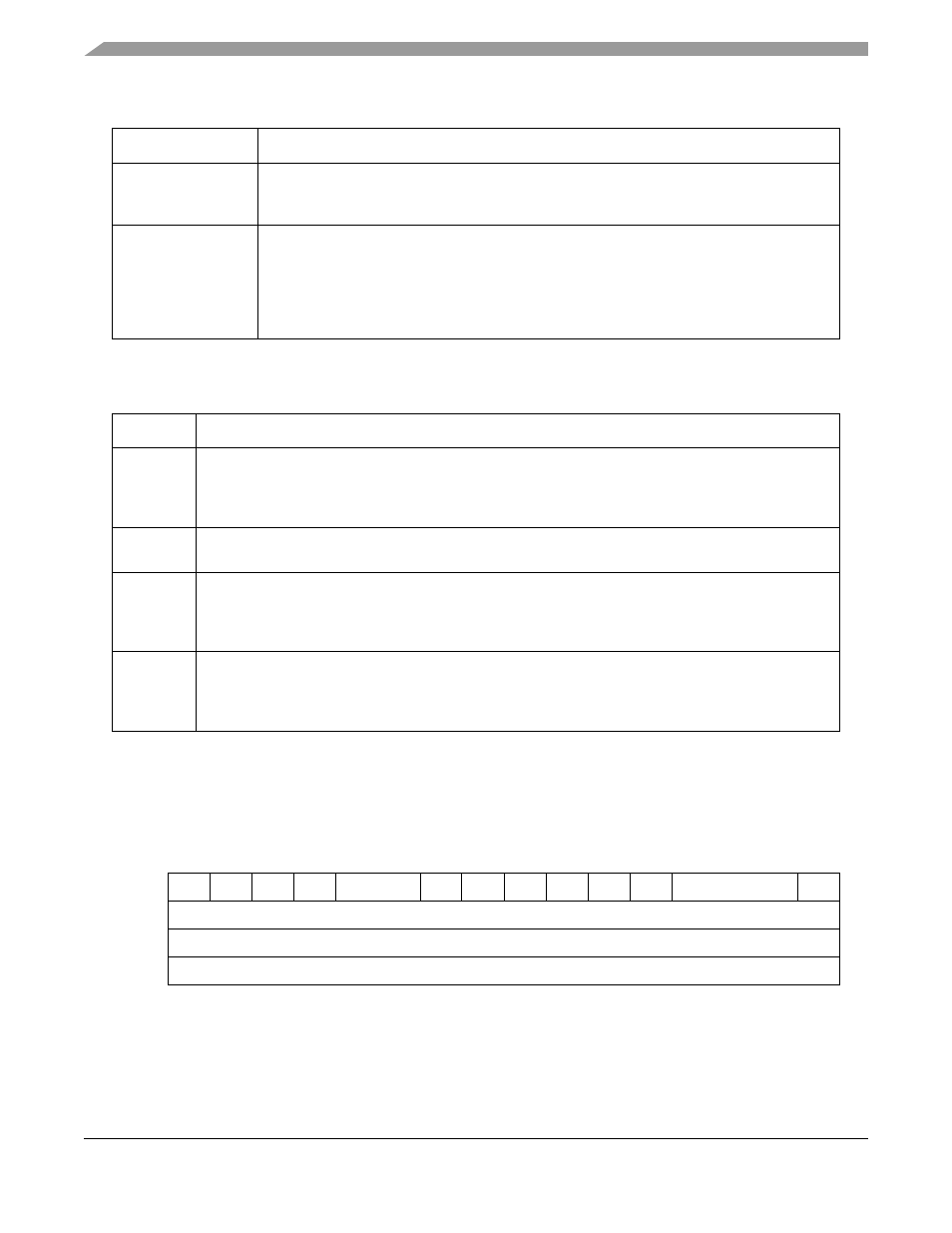

0

1

2

3

4

5

6

7

8

9

10

11

12

14

15

Field HBC

FC

RSH

IAM

CRC

PRO BRO

SBT

LPB

—

LCW

NIB

FDE

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x0x11A08 (PSMR1); 0x0x11A28 (PSMR2); 0x0x11A48 (PSMR3); 0x0x11A68 (PSMR4)

Figure 25-5. Ethernet Mode Register (PSMR)

Table 25-4. Transmission Errors (continued)

Error

Description