Freescale Semiconductor MPC8260 User Manual

Page 595

Serial Interface with Time-Slot Assigner

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

15-19

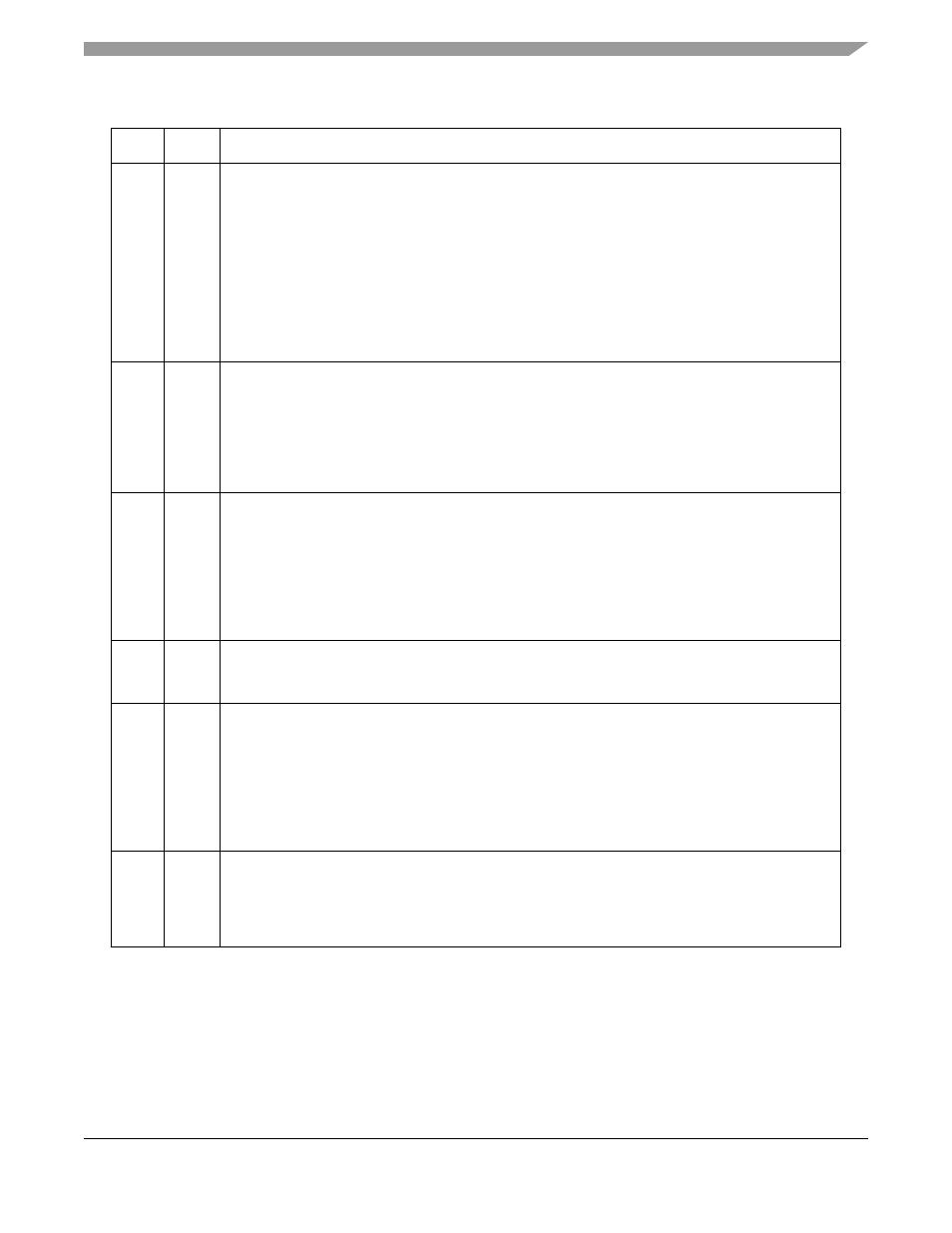

6–7

RFSDx Receive frame sync delay for TDM a, b, c, or d. Determines the number of clock delays between the

receive sync and the first bit of the receive frame. Even if CRTx is set, these bits do not control the

delay for the transmit frame.

00 No bit delay. The first bit of the frame is transmitted/received on the same clock as the sync; use

for GCI. If frame sync delay is not used and if a frame sync is issued early during the last bit of

the previous frame, data corruption could occur on all subsequent frames. To avoid this problem,

program a 1, 2, or 3-bit sync delay.

01 1-bit delay. Use for IDL

10 2-bit delay

11 3-bit delay

and

show how these bits are used.

8

DSCx

Double speed clock for TDM a, b, c or d. Some TDMs, such as GCI, define the input clock to be twice

as fast as the data rate and this bit controls this option.

0 The channel clock (L1RCLKx and/or L1TCLKx) is equal to the data clock. Use for IDL and most

TDM formats.

1 The channel clock rate is twice the data rate. Use for GCI.

Note: When an SI is in 2X mode (DSC=1), the SI does not ignore sync signals asserted in the last

phase of the last clock cycle of the frame.

9

CRTx

Common receive and transmit pins for TDM a, b, c or d. Useful when the transmit and receive

sections of a given TDM use the same clock and sync signals. In this mode, L1TCLKx and

L1TSYNCx can be used for their alternate functions.

0 Separate pins. The receive section of this TDM uses L1RCLKx and L1RSYNCx pins for framing

and the transmit section uses L1TCLKx and L1TSYNCx for framing.

1 Common pins. The receive and transmit sections of this TDM use L1RCLKx as clock pin of

channel x and L1RSYNCx as the receive and transmit sync pin. Use for IDL and GCI. RFSD and

TFSD are independent of one another in this mode.

10

SLx

Sync level for TDM a, b, c, or d.

0 The L1RSYNCx and L1TSYNCx signals are active on logic “1”.

1 The L1RSYNCx and L1TSYNCx signals are active on logic “0”.

11

CEx

Clock edge for TDM a, b, c or d. The function depends on DSCx.

When DSCx = 0:

0 The data is sent on the rising edge of the clock and received on the falling edge (use for IDL).

1 The data is sent on the falling edge of the clock and received on the rising edge.

When DSCx = 1:

0 The data is sent on the rising edge of the clock and received on the rising edge.

1 The data is sent on the falling edge of the clock and received on the falling edge (use for GCI).

See

and

12

FEx

Frame sync edge for TDM a, b, c or d. Determines whether L1RSYNCx and L1TSYNCx pulses are

sampled with the falling/rising edge of the channel clock. See

,

,

.

0 Falling edge. Use for IDL and GCI.

1 Rising edge.

Table 15-5. SI

xMR Field Descriptions (continued)

Bits

Name

Description