8 sssar receive buffer descriptor, Figure 32-21. sssar receive buffer descriptor, Sssar receive buffer descriptor -33 – Freescale Semiconductor MPC8260 User Manual

Page 1095

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

32-33

32.4.4.8

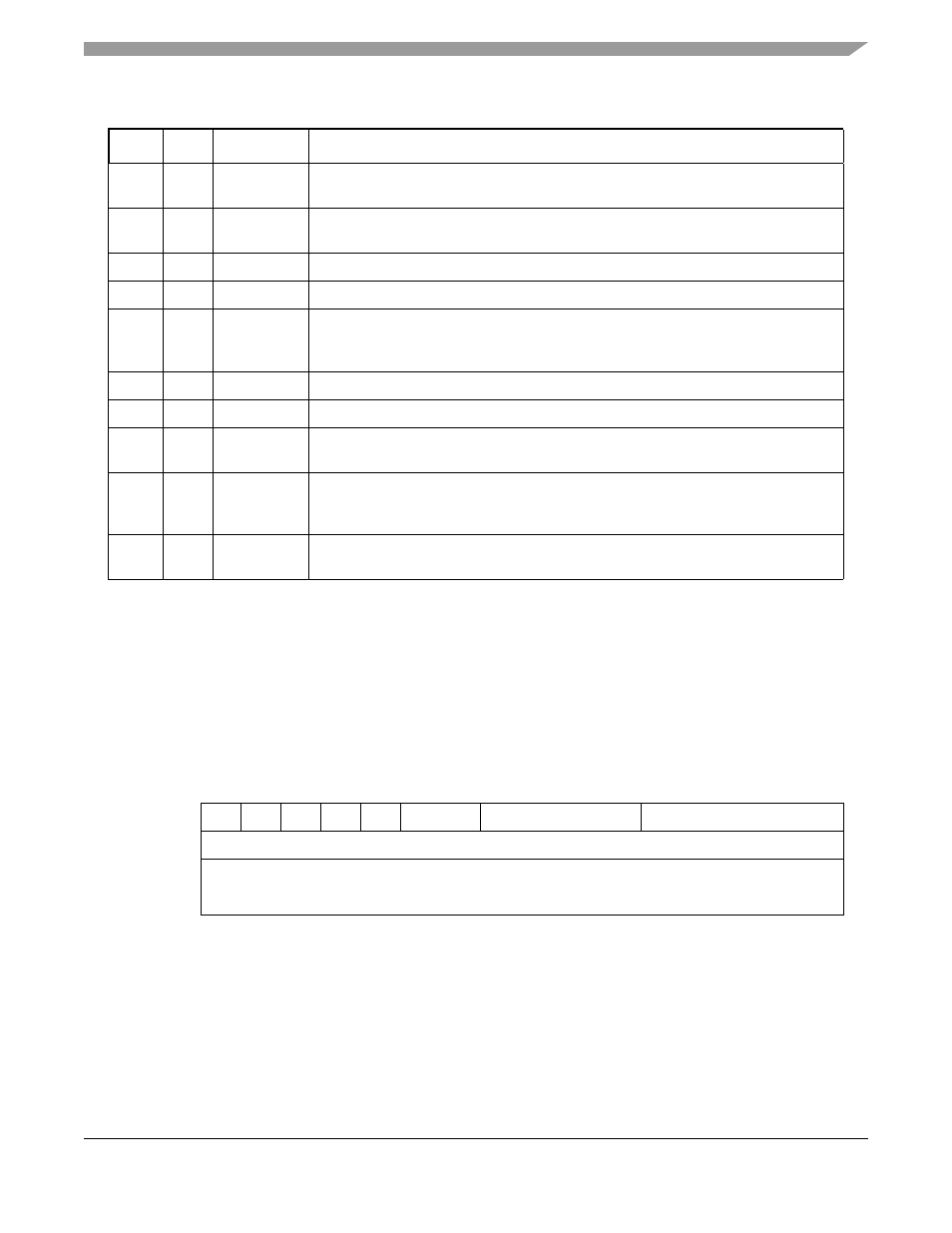

SSSAR Receive Buffer Descriptor

The SSSAR SDU is stored in a BD-buffer structure similar to the structures used for AAL5 frames. The

buffer size is determined by SSSAR RxQD[MRBLR]; the actual buffer space used may be smaller. If the

received SSSAR SDU is greater than MRBLR, the SDU spans over multiple buffers.

The SSSAR RxBD is shown in

.

describes the SSSAR RxBD fields.

0x02

—

RxBD Table

Offset

Points to the next BD to be handled by the CP. The user should initialize this pointer to

zero.

0x04 —

RxBD Table

Base

Points to the beginning of the BD table.

0x08

—

—

Reserved, should be cleared during initialization.

0x0A

—

—

Reserved, should be cleared during initialization.

0x0C

—

Time Stamp

Used for reassembly timeout of the SSSAR SDU. Whenever the first packet of an

SSSAR SDU arrives the timestamp timer is sampled and stored here (regardless of

the RasT bit).

0x10

—

—

Reserved, should be cleared during initialization.

0x12

—

—

Reserved, should be cleared during initialization.

0x14

—

MRBLR

Maximum receive buffer length. Holds the maximum receive buffer length. The actual

buffer size can be less.

0x16

—

Max_SSSAR

_SDU_

Length

Holds the maximum SSSAR SDU length. Upon each new packet the accumulated

frame size is compared with this value. If the limit is exceeded, the CP discards the rest

of the packets of the current frame.

0x18–

0x1E

—

—

Reserved, should be cleared during initialization.

1

Boldfaced entries must be initialized by the user.

0

1

2

3

4

5

6

7

10

11

15

Offset + 0x00

E

CM

W

I

L

RxError

—

UUI

Offset + 0x02

Data Length (DL)

Offset + 0x04

Rx Data Buffer Pointer (RXDBPTR)

Offset + 0x06

Figure 32-21. SSSAR Receive Buffer Descriptor

Table 32-11. SSSAR RxQD Field Descriptions (continued)

Offset

Bits

Name

1

Description