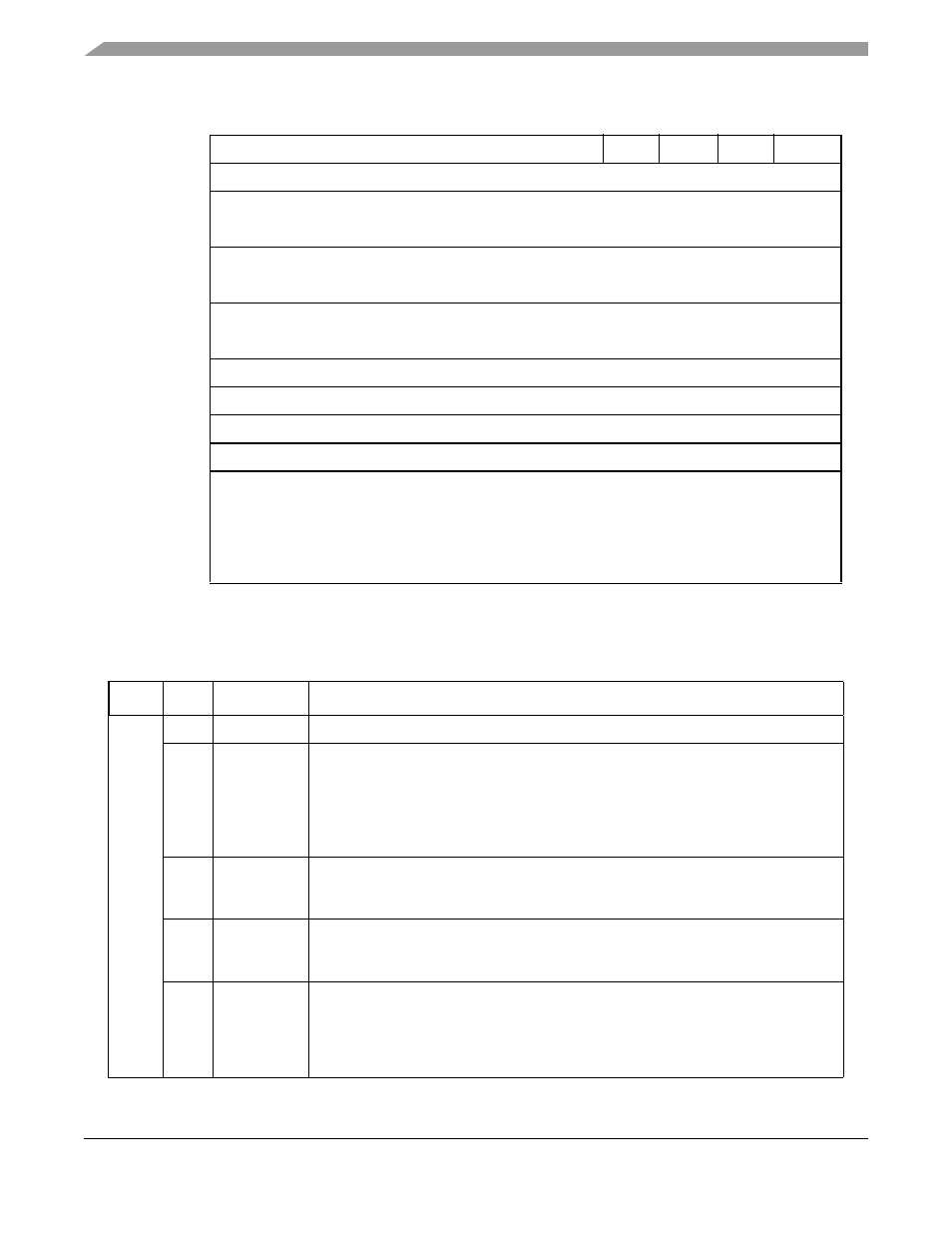

Figure 32-20. sssar rx queue descriptor, Sssar rx queue descriptor -32, Sssar rxqd field descriptions -32 – Freescale Semiconductor MPC8260 User Manual

Page 1094: Hown in, Figure 32-20, Table 32-11 describes the sssar rxqd fields

ATM AAL2

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

32-32

Freescale Semiconductor

describes the SSSAR RxQD fields.

.

0

10

11

12

13

14

15

Offset + 0x00

—

RasT

RBM

RFM

SubType

Offset + 0x02

RxBD Table Offset

Offset + 0x04

RxBD Table Base

Offset + 0x06

Offset + 0x08

—

Offset + 0x0A

Offset + 0x0c

Time Stamp

Offset + 0x0e

Offset + 0x10

—

Offset + 0x12

—

Offset + 0x14

MRBLR

Offset + 0x16

Max_SSSAR_SDU_Length

Offset + 0x18

—

Offset + 0x1A

Offset + 0x1C

Offset + 0x1E

Figure 32-20. SSSAR Rx Queue Descriptor

Table 32-11. SSSAR RxQD Field Descriptions

Offset

Bits

Name

1

Description

0x00

0–10

—

Reserved, should be cleared during initialization.

11

RasT

Ras Timer enable.

0 Ras Timer disabled (Time Stamp field is still valid)

1 Ras Timer enabled. The Ras Timer duration is set by the Ras Timer Duration

parameter in the parameter RAM. If the current SSSAR SDU is not completed

before the RasTimer expires, the BD is closed showing the Ras_Timer expired (TE)

(SSSAR RxBD[RxError] = 01) and the next packet starts a new SDU.

12

RBM

Receive buffer mask.

0 Disable receive buffer interrupt

1 Enable receive buffer interrupt

13

RFM

Receive frame mask.

0 Disable receive frame interrupt

1 Enable receive frame interrupt

14-15

SubType

Sublayer type. Should be 10 (SSSAR) for this descriptor.

00 CPS sublayer

01 CPS switched

10 SSSAR

11 Reserved