2 dma segment descriptors, Table 9-73. dma segment descriptor fields, Dma segment descriptors -95 – Freescale Semiconductor MPC8260 User Manual

Page 401: Dma segment descriptor fields -95, Section 9.13.2, “dma segment, Descriptors

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-95

9.13.2

DMA Segment Descriptors

DMA segment descriptors contain the source and destination addresses of the data segment, the segment

byte count, and a link to the next descriptor. Segment descriptors are built on cache-line (32-byte)

boundaries in either 60x or PCI memory and are linked together into chains using the

next-descriptor-address field.

Application software initializes the current descriptor address register (DMACDARx) to point to the first

descriptor in the chain. For each descriptor in the chain, the DMA controller starts a new DMA transfer

with the control parameters specified by the descriptor. The DMA controller traverses the descriptor chain

until reaching the last descriptor (with its EOTD bit set).

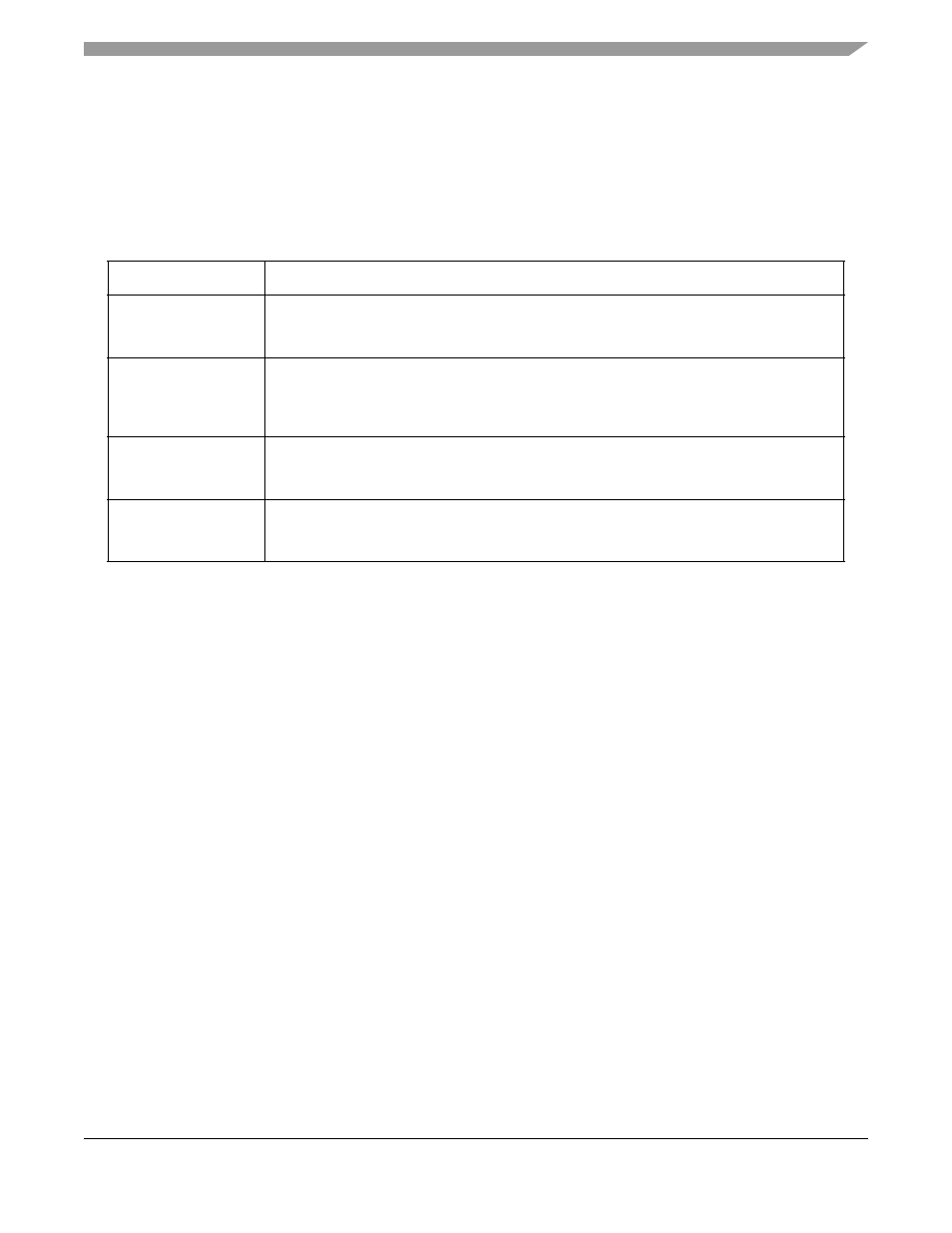

Table 9-73. DMA Segment Descriptor Fields

Descriptor Field

Description

Source address

Contains the source address of the DMA transfer. After the DMA controller reads the

descriptor from memory, this field will be loaded into the source address register. For the bit

definition, refer to

Section 9.13.1.6.4, “DMA Source Address Register [0–3] (DMASARx)

Destination address

Contains the destination address of the DMA transfer. After the DMA controller reads the

descriptor from memory, this field will be loaded into the destination address register. For the

bit definition, refer to

Section 9.13.1.6.5, “DMA Destination Address Register [0–3]

.”

Next descriptor address Points to the next descriptor in memory. After the DMA controller reads the descriptor from

memory, this field will be loaded into the next descriptor address register. For the bit definition,

refer to

Section 9.13.1.6.7, “DMA Next Descriptor Address Register [0–3] (DMANDARx)

.”

Byte count

Contains the number of bytes to transfer. After the DMA controller reads the descriptor from

memory, this field will be loaded into the byte count register. For the bit definition, refer to

Section 9.13.1.6.6, “DMA Byte Count Register [0–3] (DMABCRx)

.”