Table 11-26. 60x address bus partition, 60x address bus partition -50 – Freescale Semiconductor MPC8260 User Manual

Page 468

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

11-50

Freescale Semiconductor

Because AP alternates with A[7] of the row lines, set PSDMR[SDA10] = 011. This outputs A[7] on the

SDA10 line during the

ACTIVATE

command and AP during

READ

/

WRITE

and CBR commands.

shows the register configuration. Not shown are PSRT and MPTPR, which should be

programmed according to the device refresh requirements:

11.4.13 SDRAM Configuration Example (Bank-Based Interleaving)

Consider the following SDRAM organization:

•

Eight 64 Mbit devices, each organized as 8M x 8bits

•

Each device has four internal banks, 12 rows, and 9 columns

For bank-based Interleaving, this means that the address bus should be partitioned as shown in

Table 11-26..

The following parameters can be extracted:

•

PSDMR[PBI] = 0

•

ORx[BPD] = 01—4 internal banks

•

ORx[ROWST] = 0100—row starts at A[8]

•

ORx[NUMR] = 011—there are 12 row lines

Table 11-25. Register Settings (Page-Based Interleaving)

Register

Settings

BR

x

BA Base address

PS00 = 64-bit port size

DECC00

WP0

MS010 = SDRAM-60x bus

EMEMC0

ATOM00

DR0

V 1

OR

x

AM1111_1100_0000

LSDAM00000

BPD01

ROWST0110

NUMR011

PMSEL0

IBID0

PSDMR

PBI1

RFEN1

OP000

SDAM011

BSMA010

SDA10011

RFRC from device data sheet

PRETOACT from device data sheet

ACTTOROW from device data sheet

BL 0

LDOTOPRE from device data sheet

WRC from device data sheet

EAMUX0

BUFCMD0

CL from device data sheet

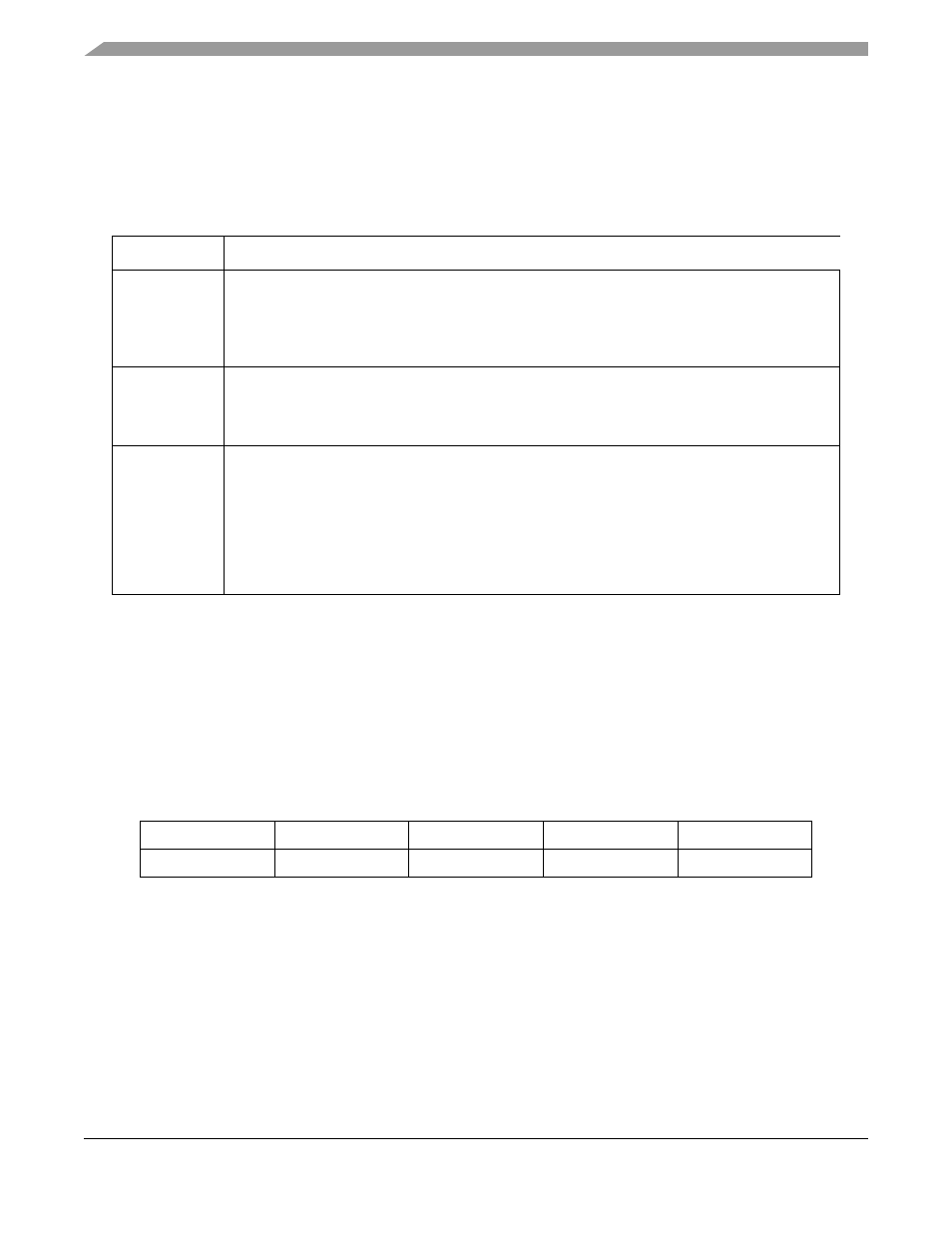

Table 11-26. 60x Address Bus Partition

A[0–5]

A[6–7]

A[8–19]

A[20–28]

A[29–31]

msb of start address Internal bank select

Row

Column

lsb