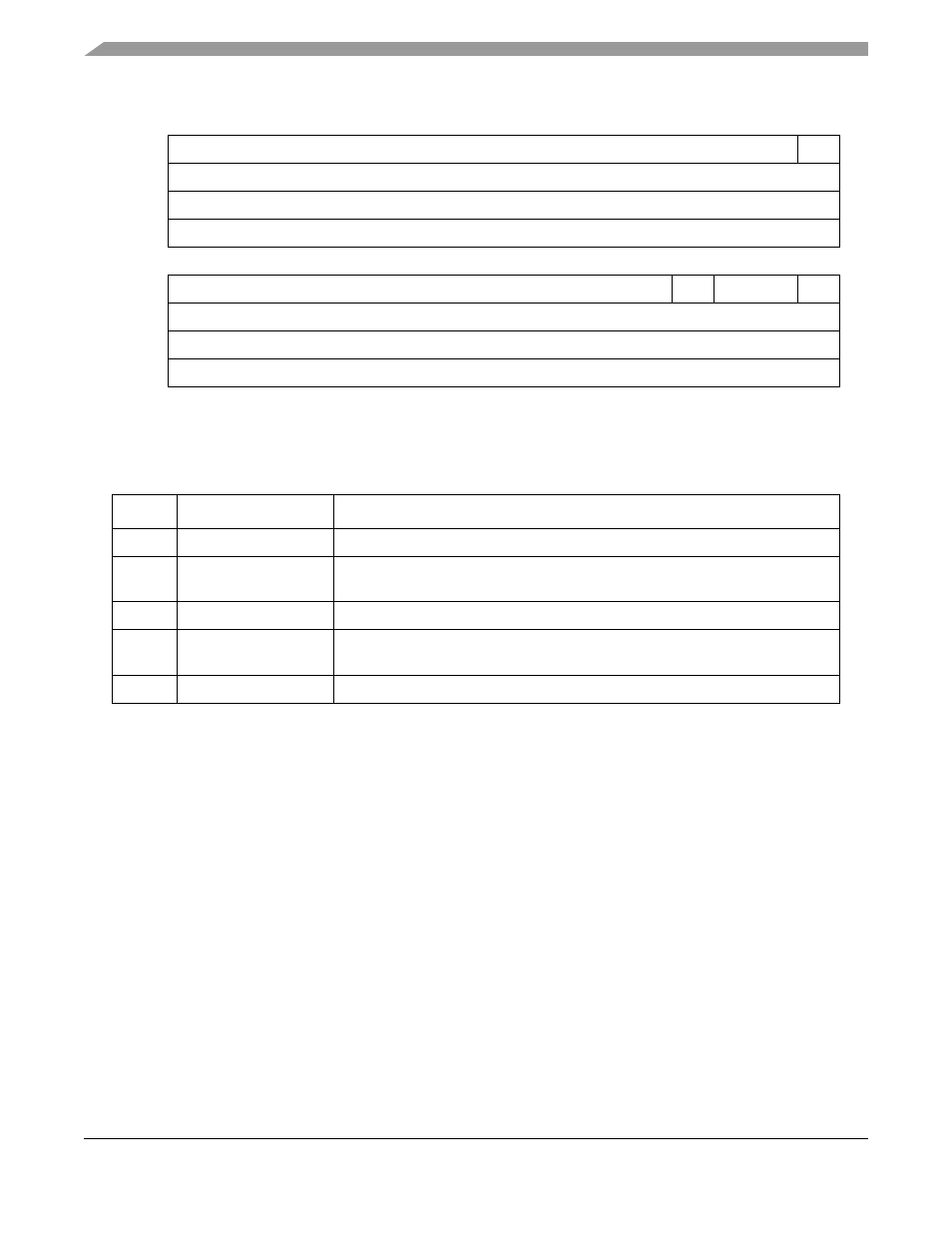

Table 9-32. pimmrbar field descriptions, Pimmrbar field descriptions -54, Registers (gplabarx) – Freescale Semiconductor MPC8260 User Manual

Page 360: Table 9-32 describes pimmrbar fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-54

Freescale Semiconductor

Figure 9-45. PCI Bus Internal Memory-Mapped Registers Base Address Register (PIMMRBAR)

describes PIMMRBAR fields.

9.11.2.14 General Purpose Local Access Base Address Registers (GPLABAR

x)

Two general purpose local access base address registers (GPLABARx) are provided to allow access to

local memory space. These registers are closely tied to PIBARx and PICMRx (see

Inbound Base Address Registers (PIBARx),”

Section 9.11.1.17, “PCI Inbound Comparison Mask

). A write to GPLABARx causes a write to PIBARx but only to the bits allowed by

the PICMRx mask. Similarly, a write to PIBARx causes a write to GPLABARx of the non-masked bits of

the base address. GPLABARx is shown in

31

17

16

Field

BA

BA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x12

15

4

3

2

1

0

Field

BA

PRE

T

MSI

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x10

Table 9-32. PIMMRBAR Field Descriptions

Bits

Name

Description

31–17

Base address

Indicates the base address for the inbound configuration window.

16–4

Base address

Hardwired to zeros, indicating that the PCI bridge requires a 128-KByte space for

the configuration registers.

3

Prefetchable

Hardwired to 0 to indicate that this address region is not prefetchable.

2–1

Type

Hardwired to 00 to indicate that the address can be located anywhere in 32-bit

address space.

0

Memory space indicator Address is mapped to memory space.