Freescale Semiconductor MPC8260 User Manual

Page 1307

Reference Manual (Rev 1) Errata

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

B-5

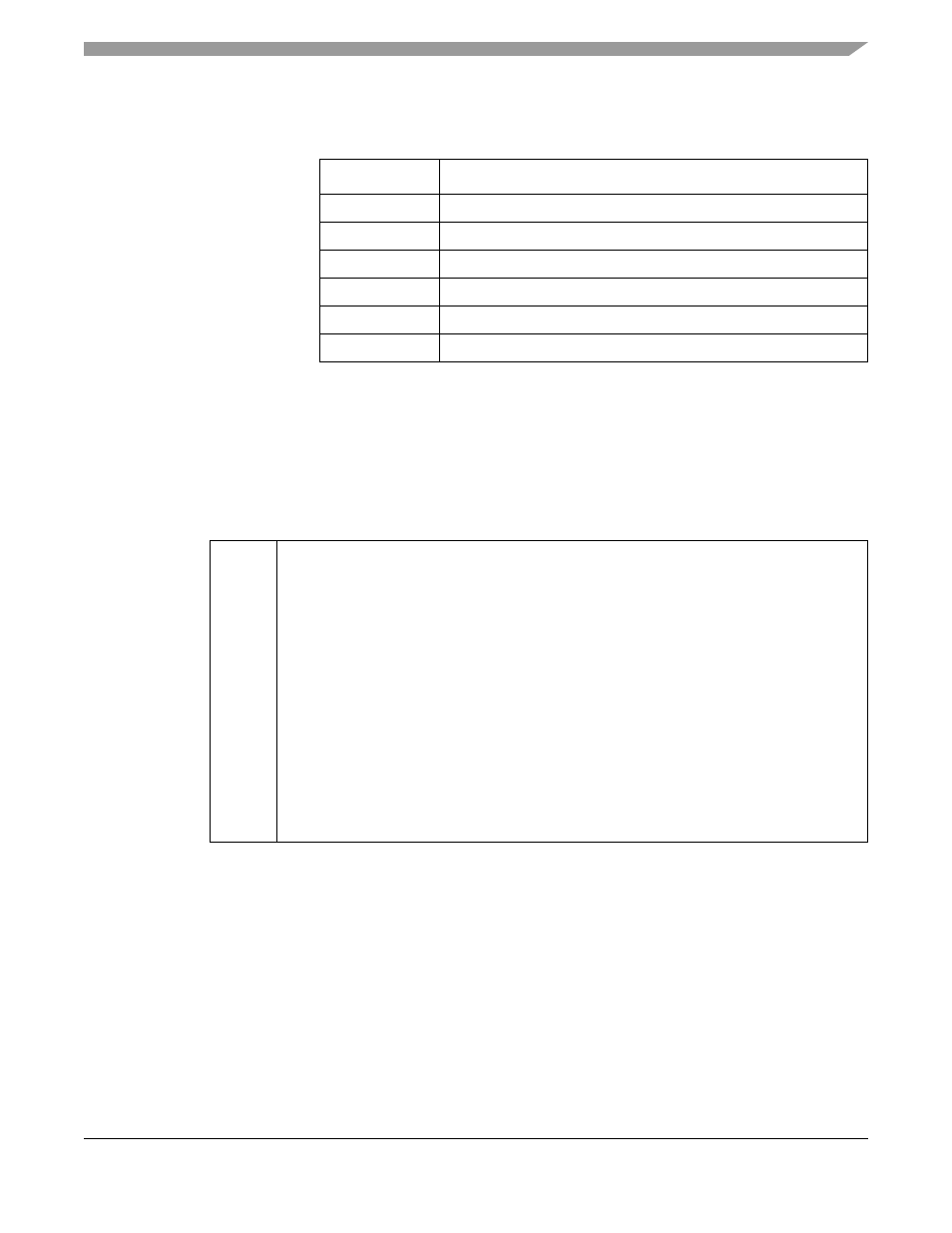

#24 as shown). IDMA option 3 is shown correctly as the last request in

prioritization of CPM peripherals. The table should appear as follows:

14.3.7, 14-10

In Table 14-3, the description for RCCR[ERAM] pertaining to HiP4 devices

(ERAM = 16–19), the starting offset for all of the additional 8 Kbytes of dual-port

RAM should be 0x4000 (not 0x0000). Also, it should read “RAM microcode

execution...”. The description should appear as follows (changes in boldface):

14.3.10, 14-12

Replace the current paragraph with the following.

Associated with each version of CPM microcode is a number (REV_NUM) that

uniquely identifies that specific microcode. This number is hard-coded into the

microcode which is stored in the CPM’s internal ROM. At power-up, the

communication processor (CP) reads this number and proceeds to store it into the

miscellaneous parameter RAM portion of the CPM's internal dual-port RAM

(DPR). The user can then access this location in DPR to determine which version

of CPM microcode is contained in that device. Table 14-5 describes which

microcode version numbers are associated with each silicon revision.

Priority

Request

1-3

Unchanged

4

IDMA[1–4] emulation (default—option 1)

1

1

The priority of each IDMA channel is programmed independently. See the

RCCR[DR

x

QP] description in Section 14.3.7, “RISC Controller Configuration Register

(RCCR).”

5

Emergency (from FCCs, MCCs, and SCCs)

6

IDMA[1–4] emulation (option 2)

1

7-33

Same relative priority

34

IDMA[1–4] emulation (option 3)

1

ERAM

.25-

µm (HiP4) devices: ERAM[16-19]. Enable RAM microcode. Configure as instructed in the

download process of a Freescale-supplied RAM microcode package.

0000 Disable microcode program execution from the dual-port RAM. (That is, microcode

execution starts at ROM address 0x0000 after reset.)

In the following configurations, RAM microcode execution starts at address 0x0000 after reset:

0010 Microcode uses the first 2 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

0100 Microcode uses the first 4 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

0110 Microcode uses the first 6 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

1000 Microcode uses the first 8 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

1010 Microcode uses the first 10 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

1100 Microcode uses the first 12 Kbytes of the dual-port RAM + 8 Kbytes starting from 0x4000.

In the following configurations, microcode execution starts at RAM address 0x4000 after reset:

0011 Microcode uses 2 Kbytes starting from dual-port RAM address 0x4000.

0101 Microcode uses 4 Kbytes starting from dual-port RAM address 0x4000.

0111 Microcode uses 6 Kbytes starting from dual-port RAM address 0x4000.

1001 Microcode uses 8 Kbytes starting from dual-port RAM address 0x4000.

Note: All other configurations not listed are reserved.