Freescale Semiconductor MPC8260 User Manual

Page 250

External Signals

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

6-10

Freescale Semiconductor

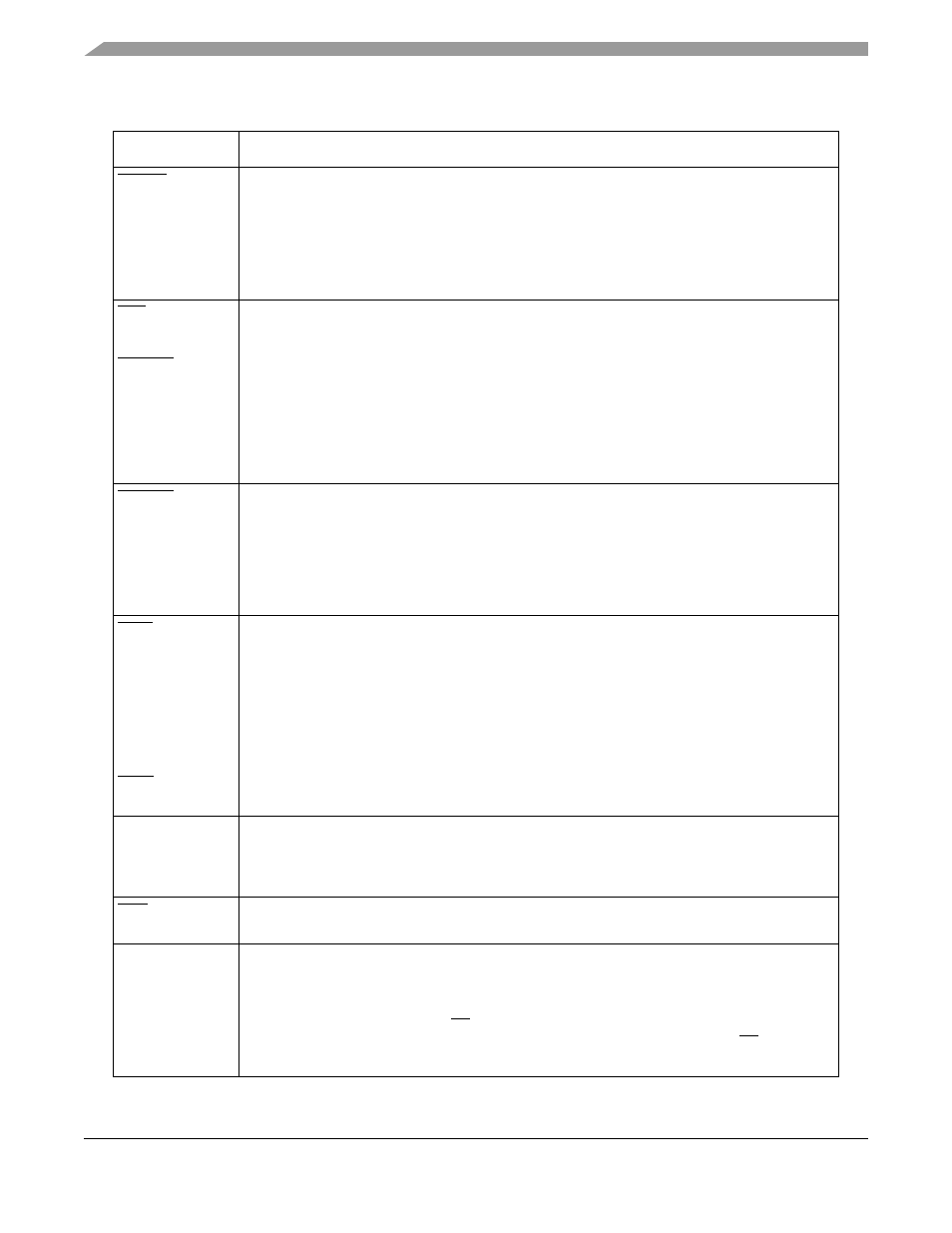

LSDWE

LGPL1

PCI_MODCK_H1

1

Local bus SDRAM write enable—Output from the local bus SDRAM controller. Should be

connected to the WE inputs of the SDRAMs.

Local bus UPM general purpose line 1—This is one of six general purpose output lines from

UPM. The values and timing of this pin is programmed in the UPM.

PCI MODCK_H1—In PCI mode, defines the operating mode of internal clock circuits.

LOE

LSDRAS

LGPL2

PCI_MODCK_H2

1

Local bus output enable—The output enable pin is an output of the Local bus GPCM. Controls

the output buffer of memory devices during read operations.

Local bus SDRAM RAS—Output from the Local bus SDRAM controller. Should be connected to

the SDRAM RAS input.

Local bus UPM general purpose line 2—This is one of six general purpose output lines from

UPM. The values and timing of this pin is programmed in the UPM.

PCI MODCK_H2—In PCI mode, defines the operating mode of internal clock circuits.

LSDCAS

LGPL3

PCI_MODCK_H3

1

Local bus SDRAM CAS—Output from the Local bus SDRAM controller. Should be connected to

the CAS inputs of the SDRAMs.

Local bus UPM general purpose line 3—This is one of six general purpose output lines from

UPM. The values and timing of this pin is programmed in the UPM.

PCI MODCK_H3—In PCI mode, defines the operating mode of internal clock circuits.

LGTA

LUPMWAIT

LGPL4

LPBS

Local bus GPCM TA—This input pin is used for transaction termination during GPCM operation.

Requires external pull up resistor for proper operation.

Local bus UPM wait—This is an input to the UPM. An external device may hold this pin high to

force the UPM to wait until the device is ready for the continuation of the operation.

Local bus UPM general purpose line 4—One of six general purpose output lines from UPM. The

values and timing of this pin is programmed in the UPM.

Local bus parity byte select—In systems in which the data parity is stored in a separate chip, this

output is used as the byte select for that chip.

LGPL5

PCI_MODCK

1

Local bus UPM general purpose line 5—This is one of six general purpose output lines from

UPM. The values and timing of this pin is programmed in the UPM.

PCI MODCK—In PCI mode, defines additional operating modes of internal clock circuits.

LWR

Local write—The local write pin is an output from the local bus memory controller. It is used to

distinguish between read and write transactions.

L_A14

PCI_PAR

1

Local bus address 14—Local bus address bit 14 output pin. In the local address bus bit 14 is most

significant and bit 31 is least significant.

PCI parity—PCI parity input/output pin. Assertion of this pin indicates that odd parity is driven

across PCI_AD[31-0] and PCI_C/BE[3–0] during address and data phases. Negation of

PCI_PAR indicates that even parity is driven across the PCI_AD[31-0] and PCI_C

/

BE[3–0] during

address and data phases.

Table 6-1. External Signals (continued)

Signal Description