Freescale Semiconductor MPC8260 User Manual

Page 130

G2 Core

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

2-12

Freescale Semiconductor

7

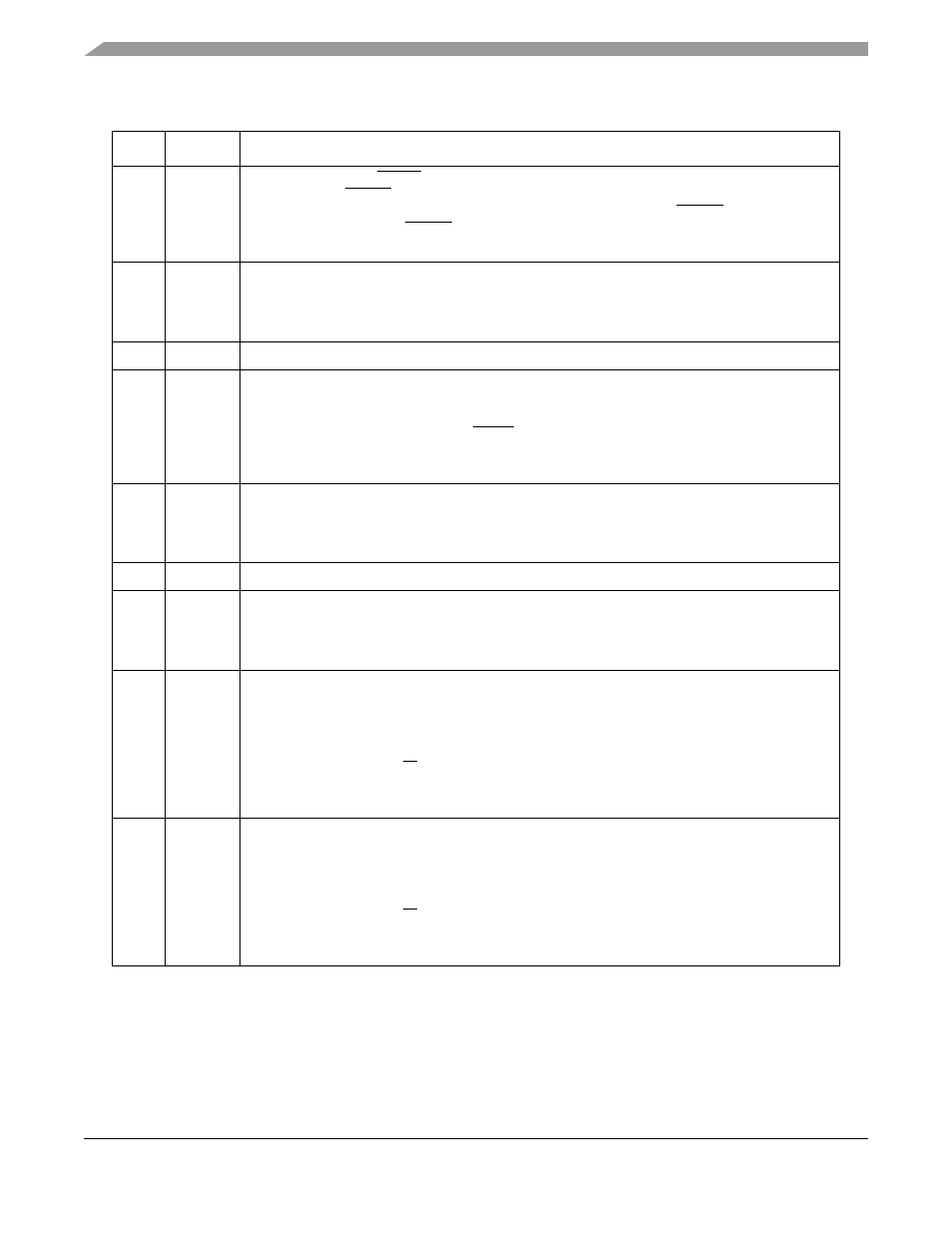

PAR

Disable precharge of ARTRY.

0 Precharge of ARTRY enabled

1 Alters bus protocol slightly by preventing the processor from driving ARTRY to high (negated)

state, allowing multiple ARTRY signals to be tied together. If this is done, the system must

restore the signals to the high state.

8

DOZE

Doze mode enable. Operates in conjunction with MSR[POW].

1

0 Doze mode disabled.

1 Doze mode enabled. Doze mode is invoked by setting MSR[POW] after this bit is set. In doze

mode, the PLL, time base, and snooping remain active.

9

—

Reserved, should be cleared.

10

SLEEP

Sleep mode enable. Operates in conjunction with MSR[POW].

1

0 Sleep mode disabled.

1 Sleep mode enabled. Sleep mode is invoked by setting MSR[POW] while this bit is set. When

this occurs, the processor asserts QREQ to indicate that it is ready to enter Sleep mode. The

main PowerQUICC II’s PLL remains active and all the internal clocks—including the core’s

clock—stop. See

Section 10.10, “Basic Power Structure.”

11

DPM

Dynamic power management enable.

1

0 Dynamic power management is disabled.

1 Functional units enter a low-power mode automatically if the unit is idle. This does not affect

operational performance and is transparent to software or any external hardware.

12–14

—

Reserved

15

NHR

Not hard reset (software-use only)—Helps software distinguish a hard reset from a soft reset.

0 A hard reset occurred if software had previously set this bit.

1 A hard reset has not occurred. If software sets this bit after a hard reset, when a reset occurs

and this bit remains set, software can tell it was a soft reset.

16

ICE

Instruction cache enable

2

0 The instruction cache is neither accessed nor updated. All pages are accessed as if they were

marked cache-inhibited (WIM = X1X). Potential cache accesses from the bus (snoop and

cache operations) are ignored. In the disabled state for the L1 caches, the cache tag state bits

are ignored and all accesses are propagated to the bus as single-beat transactions. For those

transactions, however, CI reflects the original state determined by address translation

regardless of cache disabled status. ICE is zero at power-up.

1 The instruction cache is enabled

17

DCE

Data cache enable

2

0 The data cache is neither accessed nor updated. All pages are accessed as if they were

marked cache-inhibited (WIM = X1X). Potential cache accesses from the bus (snoop and

cache operations) are ignored. In the disabled state for the L1 caches, the cache tag state bits

are ignored and all accesses are propagated to the bus as single-beat transactions. For those

transactions, however, CI reflects the original state determined by address translation

regardless of cache disabled status. DCE is zero at power-up.

1 The data cache is enabled.

Table 2-1. HID0 Field Descriptions (continued)

Bits

Name

Description