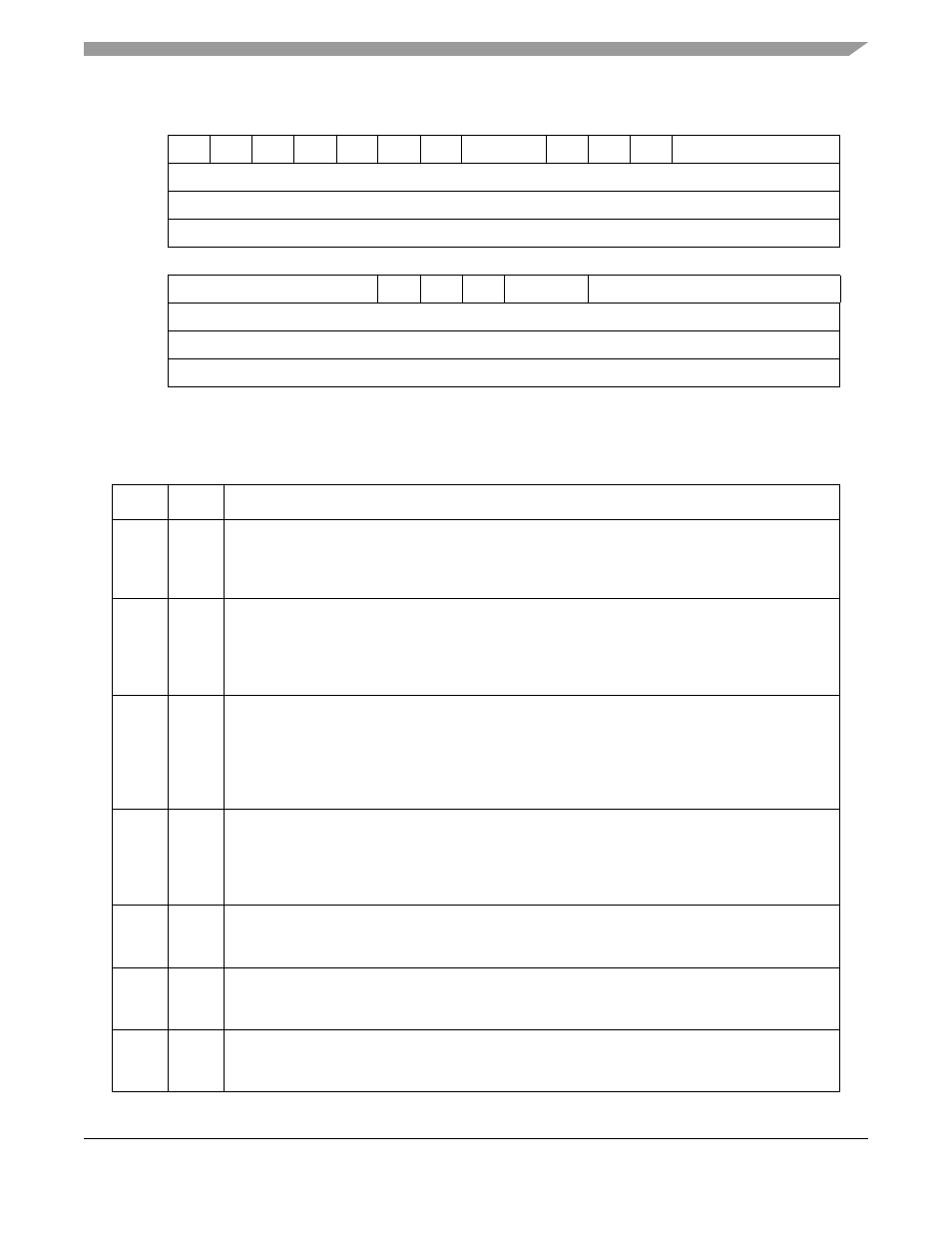

Figure 35-5. fcc ethernet mode registers (fpsmr), Fcc ethernet mode registers (fpsmr) -19, Fpsmr ethernet field descriptions -19 – Freescale Semiconductor MPC8260 User Manual

Page 1215: Hown in, Figure 35-5, Table 35-8 describes fpsmr fields

Fast Ethernet Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

35-19

describes FPSMR fields.

0

1

2

3

4

5

6

7

8

9

10

11

12

15

Field HBC

FC

SBT

LPB

LCW FDE MON

—

PRO FCE

RSH

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x0x11304 (FPSMR1), 0x0x11324 (FPSMR2), 0x0x11324 (FPSMR3)

16

20

21

22

23

24

25

26

31

Field

—

CAM BRO ECM

CRC

—

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x11306 (FPSMR1), 0x11326 (FPSMR2), 0x11326 (FPSMR3)

Figure 35-5. FCC Ethernet Mode Registers (FPSMR)

Table 35-8. FPSMR Ethernet Field Descriptions

Bits

Name

Description

0 HBC

Heartbeat

checking

0 Heartbeat checking is not performed. Do not wait for a collision after transmission.

1 Wait 40 transmit serial clocks for a collision asserted by the transceiver after transmission.

TxBD[HB] is set if the heartbeat is not heard within 40 transmit serial clocks.

1

FC

Force collision

0 Normal operation.

1 The controller forces a collision on transmission of every transmit frame. The PowerQUICC II

should be configured in loopback operation when using this feature, which allows the user to test

the PowerQUICC II collision logic. It causes the retry limit to be exceeded for each transmit frame.

2

SBT

Stop backoff timer

0 The backoff timer functions normally.

1 The backoff timer (for the random wait after a collision) is stopped whenever carrier sense is

active. In this method, the retransmission is less aggressive than the maximum allowed in the

IEEE 802.3 standard. The persistence (P_PER) feature in the parameter RAM can be used in

combination with the SBT bit (or in place of the SBT bit).

3

LPB

Local protect bit

0 Receiver is blocked when transmitter sends (default).

1 Receiver is not blocked when transmitter sends. Must be set for full-duplex operation. For

loopback operation, GFMR[DIAG] must be programmed also; see

.”

4

LCW

Late collision window

0 A late collision is any collision that occurs at least 64 bytes from the preamble.

1 A late collision is any collision that occurs at least 56 bytes from the preamble.

5

FDE

Full duplex Ethernet

0 Disable full-duplex.

1 Enable full-duplex. Must be set if FSMR[LPB] is set or external loopback is performed.

6

MON

RMON mode

0 Disable RMON mode.

1 Enable RMON mode.