Table 9-2. pci command definitions, 2 pci protocol fundamentals, Pci protocol fundamentals -7 – Freescale Semiconductor MPC8260 User Manual

Page 313: Pci command definitions -7, Bed in, Table 9-2

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-7

9.9.1.2

PCI Protocol Fundamentals

The bus transfer mechanism on the PCI bus is called a burst. A burst is comprised of an address phase and

one or more data phases.

All signals are sampled on the rising edge of the PCI clock. Each signal has a setup and hold window with

respect to the rising clock edge, in which transitions are not allowed. Outside this aperture, signal values

or transitions have no significance.

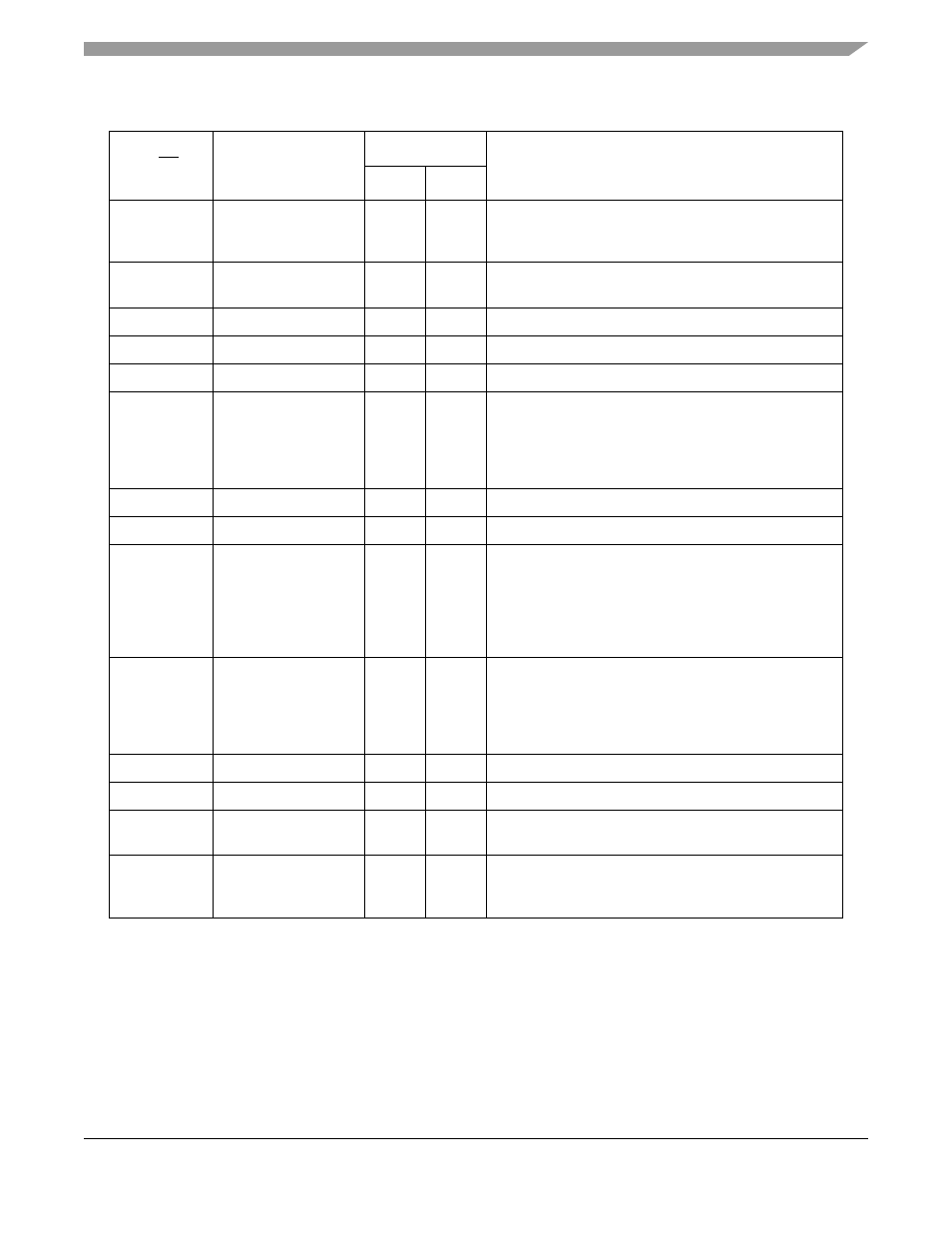

Table 9-2. PCI Command Definitions

PCI_C/BE[3-0]

Command Type

Supported as:

Definition

Initiator

Target

0b0000

Interrupt acknowledge

YES

NO

A read implicitly addressed to the system interrupt

controller. The size of the vector to be returned is

indicated on the byte enables after the address phase.

0b0001

Special cycle

YES

NO

Provides a simple message broadcast mechanism. See

Section 9.9.1.4.6, “Special Cycle Command

.”

0b0010

I/O read

YES

NO

Accesses agents mapped in I/O address space.

0b0011

I/O write

YES

NO

Accesses agents mapped in I/O address space.

0b010x

—

—

—

Reserved. No response occurs.

0b0110

Memory read

YES

YES

Accesses agents mapped in memory address space. A

read from prefetchable space, when seen as a target,

fetches a cache line of data (32 bytes) from the starting

address, even though all 32 bytes may not actually be

sent to the initiator.

0b0111

Memory write

YES

YES

Accesses agents mapped in memory address space.

0b100x

—

—

—

Reserved. No response occurs.

0b1010

Configuration read

YES

YES

Accesses the configuration space of each agent. An

agent is selected when its IDSEL signal is asserted. See

Section 9.9.1.4.4, “Host Mode Configuration Access

” for

more detail of configuration accesses. As a target, a

configuration read is only accepted if the PCI bridge is

configured to be in agent mode.

0b1011

Configuration write

YES

YES

Accesses the configuration space of each agent. An

agent is selected when its IDSEL signal is asserted. See

Section 9.9.1.4.4, “Host Mode Configuration Access

”. As

a target, a configuration write is only accepted if the PCI

bridge is configured to be in agent mode.

0b1100

Memory read multiple

YES

YES

Causes a prefetch of the next cache line.

0b1101

Dual address cycle

NO

NO

Transfers an 8 byte address to devices.

0b1110

Memory read line

YES

YES

Indicates that the initiator intends to transfer an entire

cache line of data.

0b1111

Memory write and

invalidate

NO

YES

Indicates that the initiator will transfer an entire cache line

of data, and if PCI has any cacheable memory, this line

needs to be invalidated.