Freescale Semiconductor MPC8260 User Manual

Page 443

Memory Controller

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

11-25

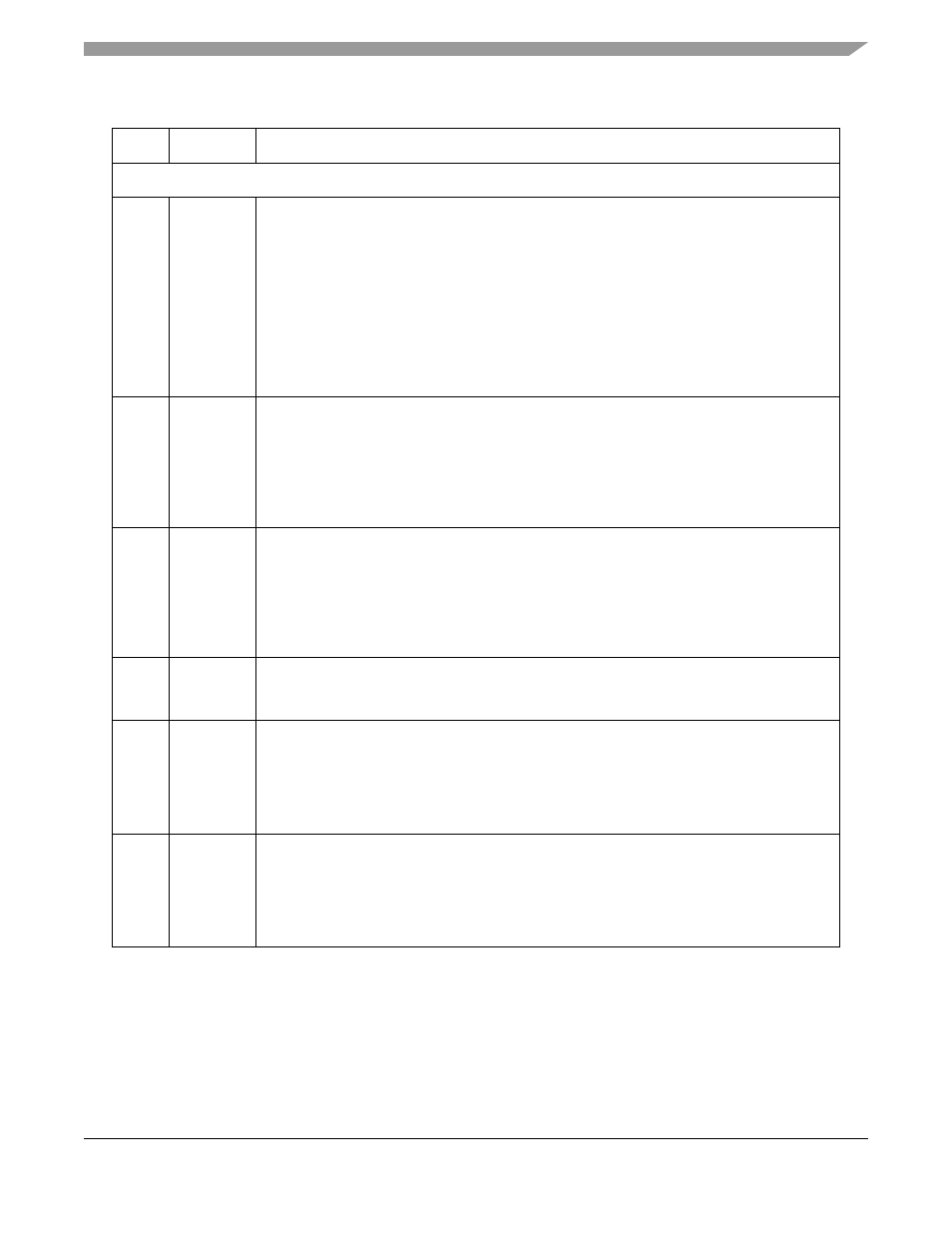

SDRAM Device–Specific Parameters:

14–16

RFRC

Refresh recovery. Defines the earliest timing for an activate command after a

REFRESH

command. Sets the refresh recovery interval in clock cycles. See

,” for how to set this field.

000 Reserved

001 3 clocks

010 4 clocks

011 5 clocks

100 6 clocks

101 7 clocks

110 8 clocks

111 16 clocks

17–19

PRETOACT Precharge to activate interval. Defines the earliest timing for

ACTIVATE

or

REFRESH

command

after a precharge command. See

Section 11.4.6.1, “Precharge-to-Activate Interval

.”

001 1 clock-cycle wait states

010 2 clock-cycle wait states

...

111 7 clock-cycle wait states

000 8 clock-cycle wait states

20–22

ACTTORW

Activate to read/write interval. Defines the earliest timing for

READ

/

WRITE

command after an

ACTIVATE

command. See

Section 11.4.6.2, “Activate to Read/Write Interval

.”

001 1 clock cycle

010 2 clock cycles

...

111 7 clock cycles

000 8 clock cycles

23

BL

Burst length

0 SDRAM burst length is 4. Use this value if the device port size is16

1 SDRAM burst length is 8. Use this value if the device port size is 32 or 8

24–25

LDOTOPRE Last data out to precharge. Defines the earliest timing for

PRECHARGE

command after the last

data was read from the SDRAM. See

Section 11.4.6.4, “Last Data Out to Precharge

.”

00 0 clock cycles

01 -1 clock cycle

10 -2 clock cycles

11 Reserved

26–27

WRC

Write recovery time. Defines the earliest timing for

PRECHARGE

command after the last data is

written to the SDRAM. See

Section 11.4.6.5, “Last Data In to Precharge—Write Recovery

.”

01 1 clock cycles

10 2 clock cycles

11 3 clock cycles

00 4 clock cycles

Table 11-9. LSDMR Field Descriptions (continued)

Bits

Name

Description