Table 9-33. gplabarx field descriptions, 15 subsystem vendor id register, Figure 9-47. subsystem vendor id register – Freescale Semiconductor MPC8260 User Manual

Page 361: Subsystem vendor id register -55, Gplabarx field descriptions -55, Figure 9-46, Table 9-33 describes gplabar x fields

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

9-55

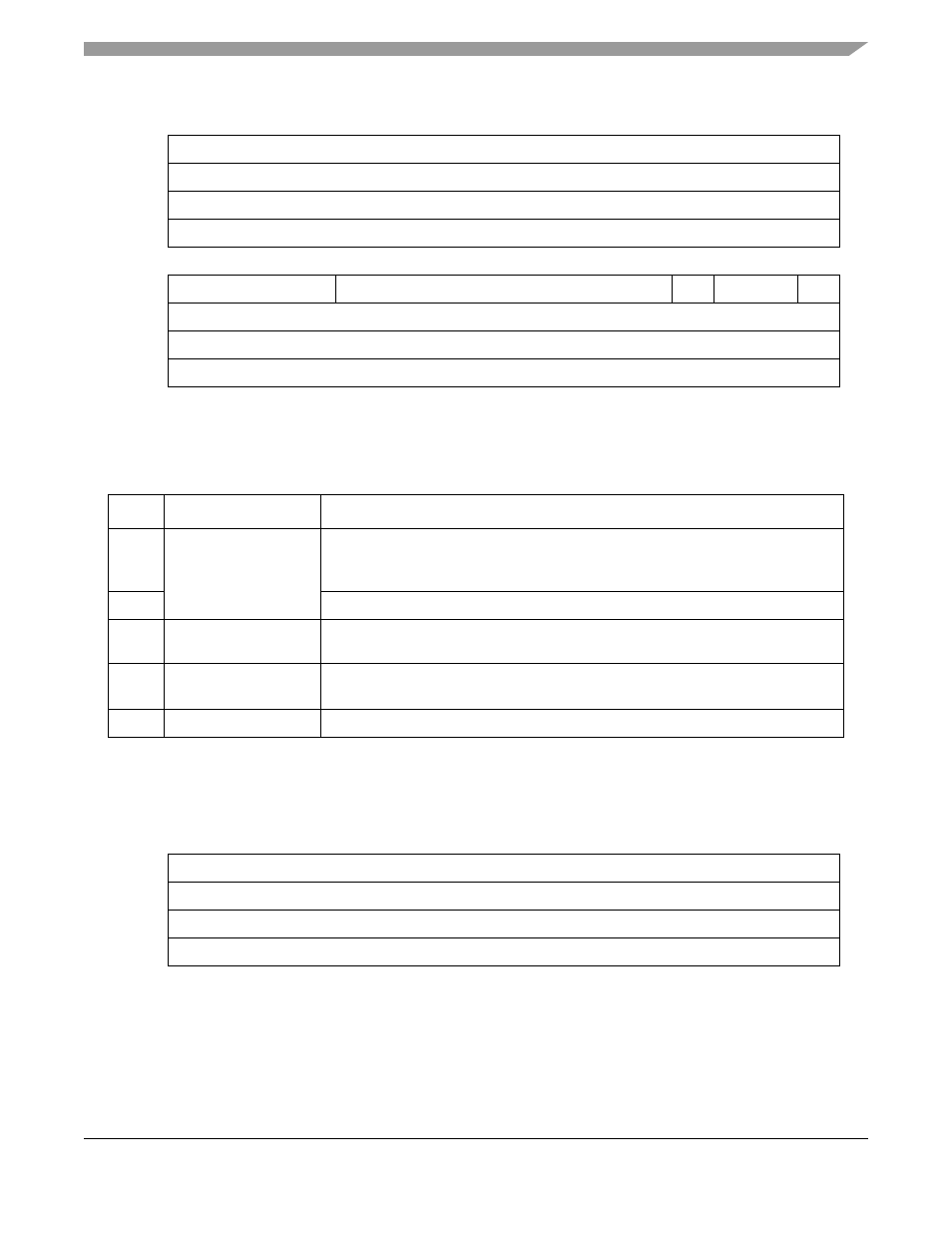

Figure 9-46. General Purpose Local Access Base Address Registers (GPLABAR

x)

describes GPLABARx fields.

9.11.2.15 Subsystem Vendor ID Register

describe the subsystem vendor ID register.

Figure 9-47. Subsystem Vendor ID Register

31

16

Field

BA

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x16 (GPLABAR0); 0x1A (GPLABAR1)

15

12

11

4

3

2

1

0

Field

BA

BA

PRE

T

MSI

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x14 (GPLABAR0); 0x18 (GPLABAR1)

Table 9-33. GPLABAR

x Field Descriptions

Bits

Name

Description

31–12

Base address

Represents the base address for the inbound GPLA

memory window. The number

of upper bits that the PCI bridge allows to be writable is selected through the PICMR;

see

Section 9.11.1.17, “PCI Inbound Comparison Mask Registers (PICMRx)

.”

11–4

Hardwired to zeros. (The minimum window size allowed is 4K.)

3

Prefetchable

Corresponds to the prefetchable bit in the PICMR; see

Inbound Comparison Mask Registers (PICMRx)

.”

2–1

Type

Hardwired to 00 to indicate that the address can be located anywhere in 32-bit

address space.

0

Memory space indicator Address is mapped to memory space (hardwired to 0).

15

0

Field

SVID

Reset

0000_0000_0000_0000

R/W

R/W

Addr

0x2C