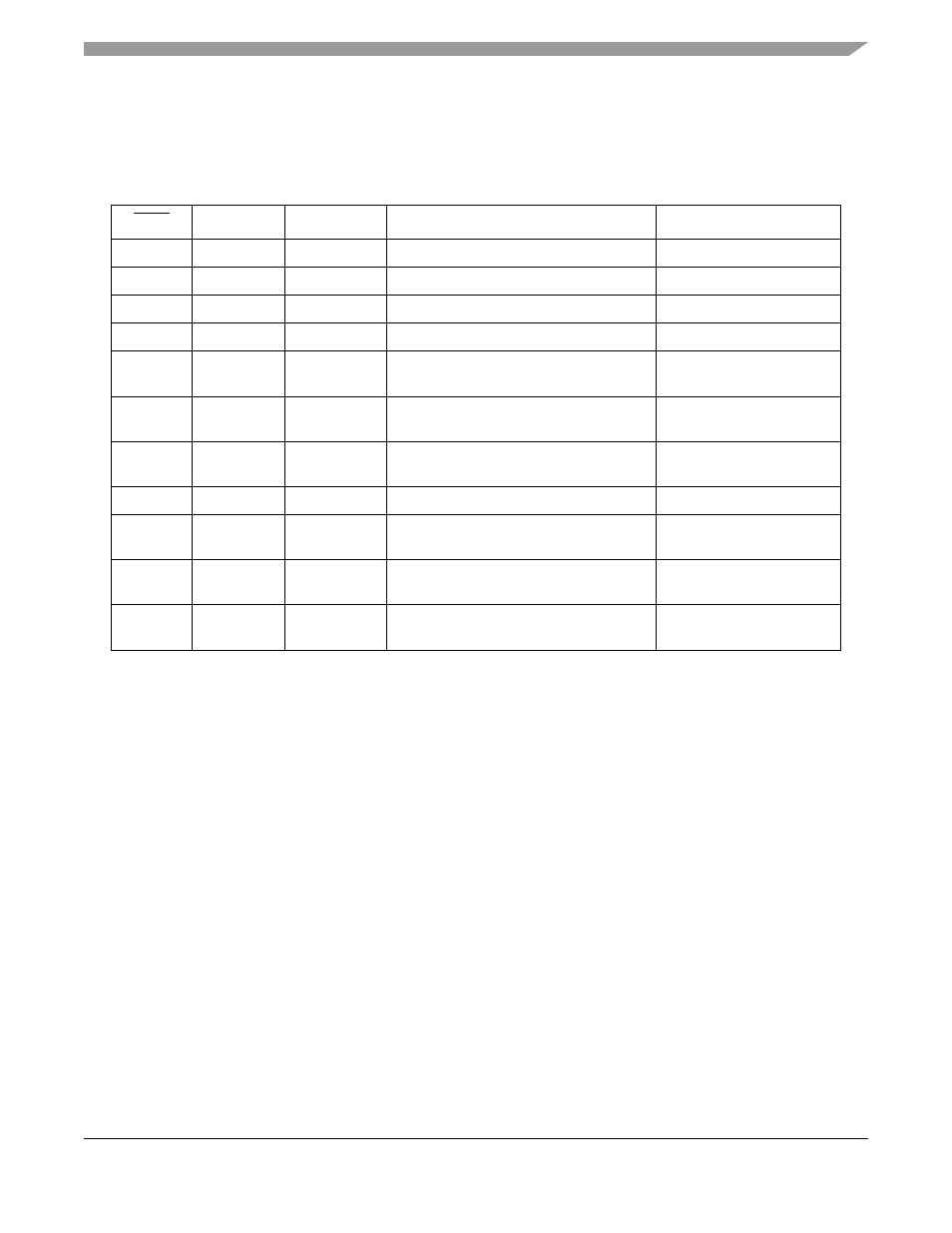

Table 8-4. transfer size signal encoding, 4 burst ordering during data transfers, Burst ordering during data transfers -13 – Freescale Semiconductor MPC8260 User Manual

Page 287: Transfer size signal encoding -13

The 60x Bus

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

Freescale Semiconductor

8-13

The PowerQUICC II supports critical-word-first burst transactions (double-word-aligned) from the

processor. The PowerQUICC II transfers the critical double word of data first, followed by the double

words from increasing addresses, wrapping back to the beginning of the eight-word block as required.

NOTE

The basic coherency size of the bus is 32 bytes for the processor

(cache-block size). Data transfers that cross an aligned 32-byte boundary

must present a new address onto the bus at that boundary for proper snoop

operation, or must operate as non-coherent with respect to the

PowerQUICC II.

8.4.3.4

Burst Ordering During Data Transfers

During burst transfers, 32 bytes of data (one cache block) are transferred to or from the cache. Burst write

transfers are performed zero double-word-first. However, because burst reads are performed

critical-double-word-first, a burst-read transfer may not start with the first double word of the cache block

and the cache-block-fill operation may wrap around the end of the cache block.

describes

PowerQUICC II burst ordering.

Table 8-4. Transfer Size Signal Encoding

TBST

TSIZ[0–3]

Transfer Size

Comments

Source

Negated

0 0 0 1

1 Byte

Byte

Core and DMA

Negated

0 0 1 0

2 Bytes

Half-word

Core and DMA

Negated

0 0 1 1

3 Bytes

—

Core and DMA

Negated

0 1 0 0

4 Bytes

Word

Core and DMA

Negated

0 1 0 1

5 Bytes

Extended 5 bytes

SDMA (PowerQUICC II

only)

Negated

0 1 1 0

6 Bytes

Extended 6 bytes

SDMA (PowerQUICC II

only)

Negated

0 1 1 1

7 Bytes

Extended 7 bytes

SDMA (PowerQUICC II

only)

Negated

0 0 0 0

8 Bytes

Double-word (maximum data bus size)

Core and DMA

Negated

1 0 0 1

16 Bytes

Extended double double-word

SDMA (PowerQUICC II

only)

Negated

1 0 1 0

24 Bytes

Extended triple double-word

SDMA (PowerQUICC II

only)

Asserted

0 0 1 0

32 bytes

Quad double-word (4 maximum data

beats)

Core and DMA