Freescale Semiconductor MPC8260 User Manual

Page 334

PCI Bridge

MPC8260 PowerQUICC II Family Reference Manual, Rev. 2

9-28

Freescale Semiconductor

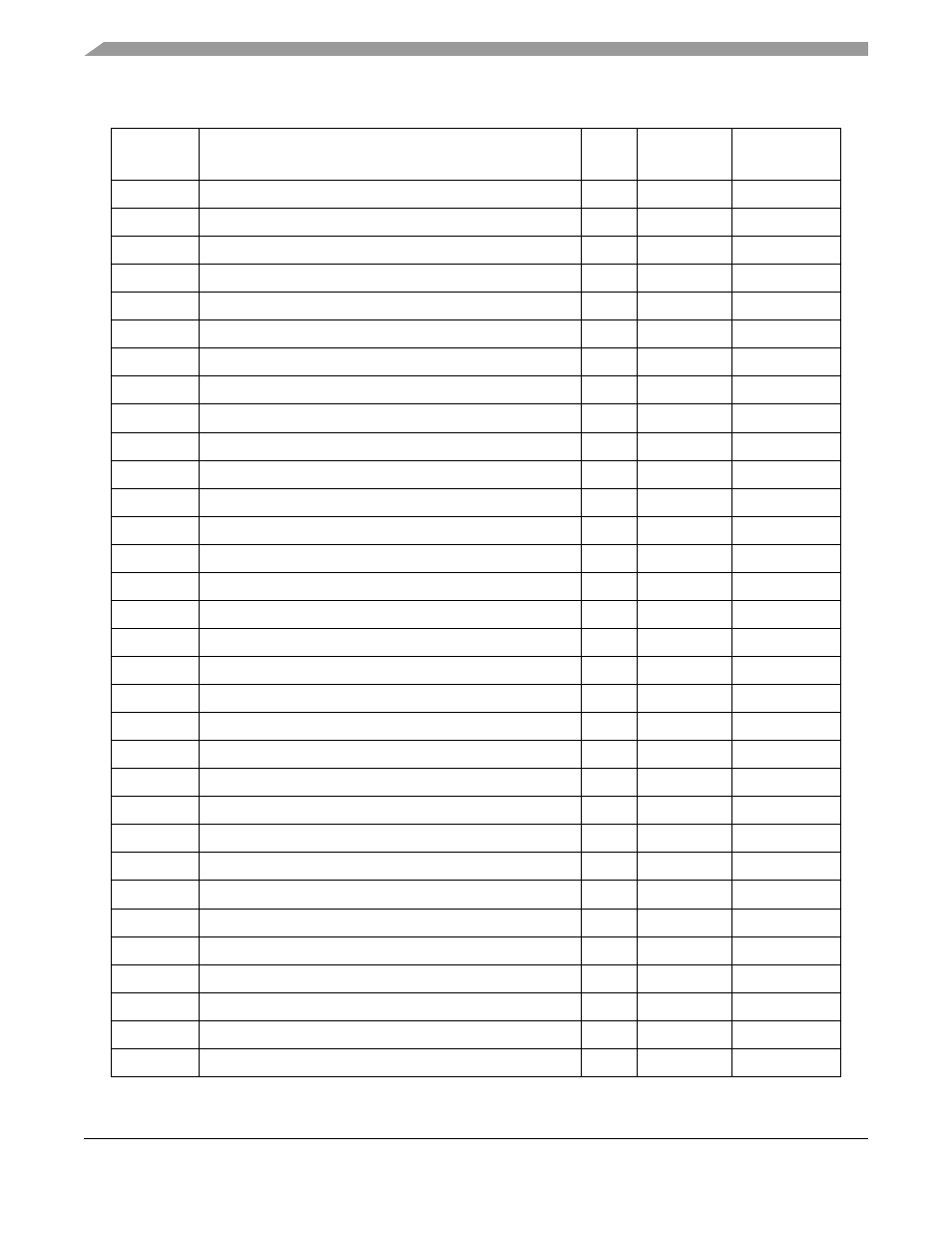

0x10458

Outbound message register 0 (OMR0)

R/W

undefined

0x1045C

Outbound message register 1 (OMR1)

R/W

undefined

0x10460

Outbound doorbell register (ODR)

R/W

0x0000_0000

0x10468

Inbound doorbell register (IDR)

R/W

0x0000_0000

0x10480

Inbound message interrupt status register (IMISR)

R/W

0x0000_0000

0x10484

Inbound message interrupt mask register (IMIMR)

R/W

0x0000_0000

0x104A0

Inbound free_FIFO head pointer register (IFHPR)

R/W

0x0000_0000

0x104A8

Inbound free_FIFO tail pointer register (IFTPR)

R/W

0x0000_0000

0x104B0

Inbound post_FIFO head pointer register (IPHPR)

R/W

0x0000_0000

0x104B8

Inbound post_FIFO tail pointer register (IPTPR)

R/W

0x0000_0000

0x104C0

Outbound free_FIFO head pointer register (OFHPR)

R/W

0x0000_0000

0x104C8

Outbound free_FIFO tail pointer register (OFTPR)

R/W

0x0000_0000

0x104D0

Outbound post_FIFO head pointer register (OPHPR)

R/W

0x0000_0000

0x104D8

Outbound post_FIFO tail pointer register (OPTPR)

R/W

0x0000_0000

0x104E4

Message unit control register (MUCR)

R/W

0x0000_0002

0x104F0

Queue base address register (QBAR)

R/W

0x0000_0000

0x10500

DMA 0 mode register (DMAMR0)

R/W

0x0000_0000

0x10504

DMA 0 status register (DMASR0)

R/W

0x0000_0000

0x10508

DMA 0 current descriptor address register (DMACDAR0)

R/W

0x0000_0000

0x10510

DMA 0 source address register (DMASAR0)

R/W

0x0000_0000

0x10518

DMA 0 destination address register (DMADAR0)

R/W

0x0000_0000

0x10520

DMA 0 byte count register (DMABCR0)

R/W

0x0000_0000

0x10524

DMA 0 next descriptor address register (DMANDAR0)

R/W

0x0000_0000

0x10580

DMA 1 mode register (DMAMR1)

R/W

0x0000_0000

0x10584

DMA 1 status register (DMASR1)

R/W

0x0000_0000

0x10588

DMA 1 current descriptor address register (DMACDAR1)

R/W

0x0000_0000

0x10590

DMA 1 source address register (DMASAR1)

R/W

0x0000_0000

0x10598

DMA 1 destination address register (DMADAR1)

R/W

0x0000_0000

0x105A0

DMA 1 byte count register (DMABCR1)

R/W

0x0000_0000

0x105A4

DMA 1 next descriptor address register (DMANDAR1)

R/W

0x0000_0000

0x10600

DMA 2 mode register (DMAMR2)

R/W

0x0000_0000

0x10604

DMA 2 status register (DMASR2)

R/W

0x0000_0000

Table 9-3. Internal Memory Map (continued)

Address

(offset)

Register

Access

Reset

Section/Page